MP2632

All-in-One, 3A Battery Charger with 3A Boost Current

The Future of Analog IC Technology

# DESCRIPTION

The MP2632 is a highly integrated, flexible, switch-mode battery charger with system powerpath management and is designed for single-cell Li-ion or Li-polymer battery use in a wide range of applications.

The IC can operate in both charge mode and boost mode to allow for full system and battery power management.

The IC has an integrated IN-to-SYS pass-through path to pass the input voltage to the system. The pass-through path has built-in over-voltage and over-current protection and has a higher priority over the charging path.

When the input power is present, the device operates in charge mode. The MP2632 detects the battery voltage automatically and charges the battery in three phases: trickle current, constant current and constant voltage. Other features include charge termination and auto-recharge. The MP2632 also integrates both input current limit and input voltage regulation to manage input power and meet the priority of the system power demand.

In the absence of an input source, the IC switches to boost mode through PB to power SYS from the battery. In boost mode, OLIM programs the output current limit, and the IC turns off at light load automatically. The IC also uses output short-circuit protection to disconnect the battery from the load completely in the event of a short-circuit fault. The MP2632 resumes normal operation once the short-circuit fault is removed.

The 4-LED driver is integrated for voltage-based fuel gauge indication. Together with torch-light control, the MP2632 provides an all-in-one solution for power banks and similar applications without an external micro-controller.

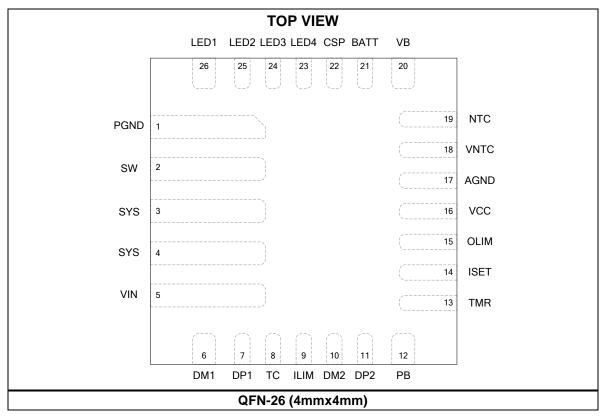

The MP2632 is available in a 26-pin QFN (4mmx4mm) package.

# **FEATURES**

- Up to 14V Sustainable Input Voltage

- 4.65V to 6V Operating Input Voltage Range

- Power Management Function, Integrated

Input Current Limit, Input Voltage Regulation

- Up to 3A Programmable Charge Current

- Trickle-Charge Function

- Selectable 4.2V/4.35V/4.45V Charge Voltage with 0.5% Accuracy

- 4-LED Driver for Battery Fuel Gauge Indication

- Automatic Turn-Off at Light Load

- Input Source Detection

- Output Source Signaling

- Torch-Light Control

- Negative Temperature Coefficient Pin for Battery Temperature Monitoring

- Programmable Timer Back-Up Protection

- Thermal Regulation and Thermal Shutdown

- Internal Battery Reverse Leakage Blocking

- Integrated Over-Voltage Protection (OVP) and Over-Current Protection (OCP) for Pass-Through Path

- Reverse Boost Operation Mode for System

Power

- Up to 3.0A Programmable Output Current Limit for Boost Mode

- Integrated Short-Circuit Protection (SCP) and Output Over-Voltage Protection for Boost Mode

# APPLICATIONS

- Sub-Battery Applications

- Power-Bank Applications for Smart Phones

- Tablets and Other Portable Devices

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

Analog Digital Adaptive Modulation (ADAM) is a trademark of Monolithic Power Systems, Inc.

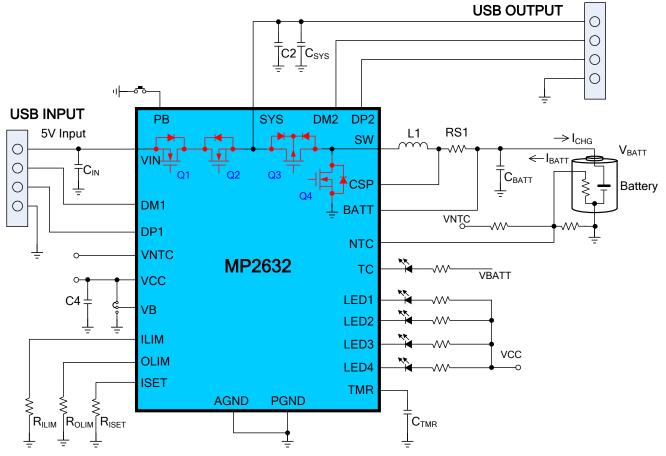

# **TYPICAL APPLICATION**

| Table 1: | Operation | Mode | Control |

|----------|-----------|------|---------|

|----------|-----------|------|---------|

| V <sub>IN</sub> (V)                | PB                        | <b>Operation Mode</b>  | Q1, Q2 | Q3  | Q4  |

|------------------------------------|---------------------------|------------------------|--------|-----|-----|

| $V_{BATT}$ + 300mV < $V_{IN}$ < 6V | Х                         | Charging               | On     | SW  | SW  |

| $V_{IN} < V_{BATT}$ + 300mV        | From H to L<br>for >1.5ms | Discharging<br>(boost) | Off    | SW  | SW  |

| V <sub>IN</sub> > 6V               | Х                         | OVP                    | Off    | Off | Off |

| V <sub>IN</sub> < 2V               | H or L                    | Sleep                  | Off    | Off | Off |

# **ORDERING INFORMATION**

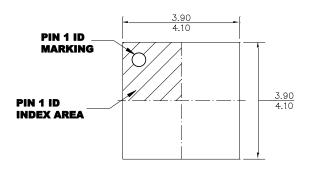

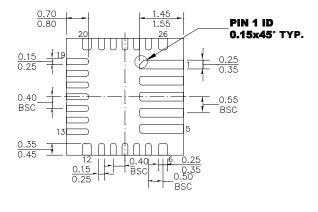

| Part Number* | Package          | Top Marking |

|--------------|------------------|-------------|

| MP2632GR     | QFN-26 (4mmx4mm) | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP2632GR–Z)

TOP MARKING MPSYWW MP2632 LLLLLL

MPS: MPS prefix Y: Year code WW: Week code MP2632: Product code of MP2632GR LLLLLL: Lot number

# PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup>

| VIN to PGND                                               |

|-----------------------------------------------------------|

| SYS to PGND0.3V to +6.5V                                  |

| SW to PGND0.3V (-2V for 20ns) to +6.5V                    |

| BATT to PGND0.3V to +6.5V                                 |

| All other pins to AGND0.3V to +6.5V                       |

| Continuous power dissipation $(T_A = +25^{\circ}C)^{(2)}$ |

|                                                           |

| Junction temperature                                      |

| Lead temperature (solder)                                 |

| Storage temperature65°C to +150°C                         |

| Recommended Operating Conditions <sup>(3)</sup>           |

| Supply voltage (V <sub>IN</sub> ) | 4.65V to +6V    |

|-----------------------------------|-----------------|

| I <sub>IN</sub>                   | Up to 3A        |

| I <sub>SYS</sub>                  | Up to 3A        |

| I <sub>CHG</sub>                  | Up to 3A        |

| V <sub>BATT</sub>                 | Up to 4.45V     |

| Operating junction temp. (TJ      | )40°C to +125°C |

# Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

QFN-26 (4mmx4mm)......44 ......9 .... °C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

### $V_{IN} = 5.0V$ , RS1 = 10m $\Omega$ , T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                       | Symbol                 | Condition                                           | Min   | Тур  | Max   | Units |

|-------------------------------------------------|------------------------|-----------------------------------------------------|-------|------|-------|-------|

| IN-to-SYS NMOS on resistance                    | R <sub>IN to SYS</sub> | VCC = 5V                                            | 49    | 55   | 62    | mΩ    |

| High-side PMOS on resistance                    | $R_{H_{DS}}$           | VCC = 5V                                            | 20    | 26   | 31    | mΩ    |

| Low-side NMOS on resistance                     | $R_{L_{DS}}$           | VCC = 5V                                            | 20    | 26   | 31    | mΩ    |

| High-side PMOS peak current                     |                        | CC charge mode/boost mode                           | 5.7   | 7    | 8.4   | Α     |

| limit                                           | I <sub>PEAK_HS</sub>   | TC charge mode                                      | 1.9   | 2.3  | 2.8   | Α     |

| Low-side NMOS peak current limit                | I <sub>PEAK_LS</sub>   |                                                     | 6.4   | 8    | 9.6   | А     |

| Switching frequency                             | F <sub>sw</sub>        |                                                     | 500   | 600  | 800   | kHz   |

| VCC UVLO                                        | V <sub>CC_UVLO</sub>   |                                                     | 1.96  | 2.16 | 2.36  | V     |

| VCC UVLO hysteresis                             |                        |                                                     |       | 100  |       | mV    |

| Charge Mode                                     |                        | ·                                                   |       |      |       | •     |

| Input quiescent current                         | I <sub>Q_IN</sub>      | Charge mode, I <sub>SYS</sub> = 0,<br>battery float |       | 1.8  | 2.5   | mA    |

|                                                 |                        | R <sub>ILIM</sub> = 88.7k                           | 380   | 435  | 490   |       |

| Input current limit for DCP                     | I <sub>IN_LIMIT</sub>  | R <sub>ILIM</sub> = 49.9k                           | 740   | 820  | 900   | mA    |

|                                                 |                        | R <sub>ILIM</sub> = 14.7k                           | 2580  | 2840 | 3100  |       |

| Input current limit for SDP                     | I <sub>USB</sub>       | SDP is detected using DP1/DM1 detection             | 400   | 450  | 500   | mA    |

| Input over-voltage protection                   | V <sub>IN_OVP</sub>    | V <sub>IN</sub> rising                              | 5.8   | 6.0  | 6.2   | V     |

| V <sub>IN_OVP</sub> hysteresis                  |                        | V <sub>IN</sub> falling                             |       | 250  |       | mV    |

| Input under-voltage lockout                     | V <sub>IN_UVLO</sub>   | V <sub>IN</sub> rising                              | 3.3   | 3.45 | 3.6   | V     |

| V <sub>UVLO</sub> hysteresis                    |                        | V <sub>IN</sub> falling                             |       | 155  |       | mV    |

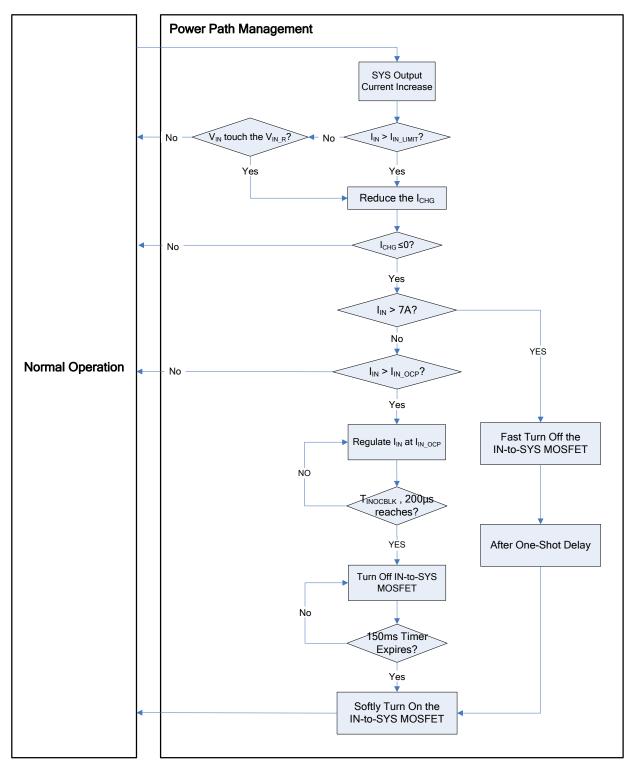

| Input over-current threshold                    | I <sub>IN_OCP</sub>    |                                                     |       | 5    |       | Α     |

| Input over-current blanking time <sup>(5)</sup> | T <sub>INOCBLK</sub>   |                                                     |       | 200  |       | μs    |

| Input over-current recover time <sup>(5)</sup>  | TINRECVR               |                                                     |       | 150  |       | ms    |

|                                                 |                        | Connect VB to GND                                   | 4.328 | 4.35 | 4.372 |       |

| Terminal battery voltage                        | V <sub>BATT_FULL</sub> | Leave VB floating                                   | 4.179 | 4.2  | 4.221 | V     |

|                                                 |                        | Connect VB to VCC                                   | 4.428 | 4.45 | 4.472 |       |

|                                                 |                        | Connect to VB to GND                                | 4.1   | 4.16 | 4.22  |       |

| Recharge threshold                              | V <sub>RECH</sub>      | Leave VB floating                                   | 3.95  | 4.02 | 4.08  | V     |

|                                                 |                        | Connect VB to VCC                                   | 4.19  | 4.26 | 4.32  | 1     |

|                                                 |                        | Connect VB to GND                                   | 3     | 3.07 | 3.13  |       |

| Trickle charge voltage threshold                | V <sub>BATT_TC</sub>   | Leave VB floating                                   | 2.9   | 2.96 | 3.02  | V     |

|                                                 |                        | Connect VB to VCC                                   | 3.07  | 3.14 | 3.2   | 1     |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN} = 5.0V$ , RS1 = 10m $\Omega$ , T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                            | Symbol                 | Condition                                                                                               | Min    | Тур    | Max    | Units                      |

|------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------|--------|--------|--------|----------------------------|

| Trickle charge hysteresis                            |                        |                                                                                                         |        | 220    |        | mV                         |

| Battery over-voltage threshold                       | V <sub>BOVP</sub>      | As a percentage of V <sub>BATT_FULL</sub>                                                               | 101.5% | 103.5% | 105.5% | V <sub>BATT_</sub><br>FULL |

|                                                      |                        | RS1 = 10mΩ,<br>R <sub>ISET</sub> = 150k                                                                 | 900    | 1000   | 1100   |                            |

| Constant charge (CC) current                         | Icc                    | RS1 = 10m $\Omega$ , R <sub>ISET</sub> = 75k                                                            | 1800   | 2000   | 2200   | mA                         |

|                                                      |                        | RS1 = 10mΩ,<br>R <sub>ISET</sub> = 49.9k                                                                | 2700   | 3000   | 3300   |                            |

| Trickle charge current                               | I <sub>TC</sub>        |                                                                                                         | 90     | 280    | 400    | mA                         |

| Termination charge current                           | I <sub>BF</sub>        | RS1 = 10mΩ                                                                                              | 90     | 200    | 300    | mA                         |

| Input voltage regulation reference                   | V <sub>REG</sub>       |                                                                                                         | 4.55   | 4.65   | 4.75   | V                          |

| Boost Mode                                           |                        |                                                                                                         |        |        |        |                            |

| SYS voltage range                                    |                        | $I_{SYS} = 100 \text{mA}$                                                                               | 5      | 5.1    | 5.2    | V                          |

| Boost SYS over-voltage protection threshold          | V <sub>SYS(OVP</sub> ) | Threshold over V <sub>SYS</sub> to<br>turn off the converter<br>during boost mode                       | 5.6    | 5.8    | 6      | V                          |

| SYS over-voltage protection threshold hysteresis     |                        | $V_{\text{SYS}}$ falling from $V_{\text{SYS}(\text{OVP})}$                                              |        | 330    |        | mV                         |

| Boost quiescent current                              | I <sub>Q_BOOST</sub>   | I <sub>SYS</sub> = 0, boost mode,<br>in test mode with auto-off<br>disabled                             |        |        | 1.65   | mA                         |

|                                                      |                        | $\begin{array}{l} \text{RS1} = 10 \text{m}\Omega, \\ \text{R}_{\text{OLIM}} = 150 \text{k} \end{array}$ | 0.9    | 1      | 1.1    |                            |

| Programmable boost output current-<br>limit accuracy | I <sub>OLIM</sub>      | RS1 = 10mΩ,<br>R <sub>OLIM</sub> = 60.4k                                                                | 2.34   | 2.5    | 2.66   | А                          |

|                                                      |                        | RS1 = 10mΩ,<br>R <sub>OLIM</sub> = 49.9k                                                                | 2.8    | 3      | 3.2    |                            |

| SYS over-current blanking time <sup>(5)</sup>        | TSYSOCBLK              |                                                                                                         |        | 150    |        | μs                         |

| SYS over-current recover time <sup>(5)</sup>         | TSYSRECVR              |                                                                                                         |        | 1.5    |        | ms                         |

| System load to turn off boost                        | I <sub>NOLOAD</sub>    | Battery current in boost mode                                                                           | 50     | 85     | 120    | mA                         |

| Light-load blanking time <sup>(5)</sup>              |                        |                                                                                                         |        | 16     |        | S                          |

| Week bettery threshold                               | V                      | During boost                                                                                            |        | 2.5    | 2.6    | V                          |

| Weak battery threshold                               | V <sub>BAT_UVLO</sub>  | Before boost starts                                                                                     |        | 2.9    | 3.05   | V                          |

| Sleep Mode                                           |                        |                                                                                                         |        |        |        |                            |

| Battery leakage current                              | I <sub>LEAKAGE</sub>   | $V_{BATT} = 4.2V$ , SYS float,<br>$V_{IN} = 0V$ ,<br>not in boost mode                                  |        | 13     | 16     | μA                         |

# ELECTRICAL CHARACTERISTICS (continued)

### $V_{IN} = 5.0V$ , RS1 = 10m $\Omega$ , T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                                    | Symbol                       | Condition                                                     | Min   | Тур   | Max   | Units            |

|--------------------------------------------------------------|------------------------------|---------------------------------------------------------------|-------|-------|-------|------------------|

| Indication and Logic                                         |                              |                                                               |       |       |       |                  |

| LED1, LED2, LED3, and LED4 output low voltage                |                              | Sinking 5mA                                                   |       |       | 200   | mV               |

| TC output low voltage                                        |                              | Sinking 100mA                                                 |       |       | 550   | mV               |

| LED1, LED2, LED3, LED4, TC leakage current                   |                              | Connected to 5V                                               |       |       | 0.2   | μA               |

| INOVP, BOVP and NTC, fault blinking frequency <sup>(5)</sup> |                              |                                                               |       | 1     |       | Hz               |

| PB input logic low voltage                                   |                              |                                                               |       |       | 0.4   | V                |

| PB input logic high voltage                                  |                              |                                                               | 1.4   |       |       | V                |

| Protection                                                   |                              |                                                               |       |       |       | ·                |

| Trickle charge time                                          |                              | $C_{TMR} = 0.1 \mu F$ , remains in TC mode, $I_{TC} = 250 mA$ |       | 16    |       | Min              |

| Total charge time                                            |                              | $C_{TMR} = 0.1 \mu F$ , $I_{CHG} = 1A$                        |       | 390   |       | Min              |

| NTC low temp, rising threshold                               |                              |                                                               | 65.2% | 66.2% | 67.2% |                  |

| NTC low temp, rising threshold hysteresis                    |                              | R <sub>NTC</sub> = NCP18XH103(0°C)                            |       | 2.4%  |       |                  |

| NTC high temp, rising threshold                              |                              |                                                               | 34.7% | 35.7% | 36.7% | V <sub>SYS</sub> |

| NTC high temp, rising threshold hysteresis                   |                              | R <sub>NTC</sub> = NCP18XH103(50°C)                           |       | 2%    |       |                  |

| Charging current foldback threshold <sup>(5)</sup>           |                              | Charge mode                                                   |       | 120   |       | °C               |

| Thermal shutdown threshold <sup>(5)</sup>                    |                              |                                                               |       | 150   |       | °C               |

| Input DP1/DM1 USB Detection                                  |                              |                                                               |       |       |       |                  |

| DP1 voltage source                                           | $V_{DP\_SRC}$                |                                                               | 0.5   | 0.6   | 0.7   | V                |

| Data connect detect current source                           | I <sub>DP_SRC</sub>          |                                                               | 7     |       | 13    | μA               |

| DM1 sink current                                             | I <sub>DM_SINK</sub>         |                                                               | 50    | 100   | 150   | μA               |

| Leakage current input DP1/DM1                                | I <sub>DP_LKG</sub>          |                                                               | -1    |       | 1     | MA               |

| Leakage current input DF 1/DM1                               | I <sub>DM_LKG</sub>          |                                                               | -1    |       | 1     | MA               |

| Data detect voltage                                          | $V_{DAT\_REF}$               |                                                               | 0.25  |       | 0.4   | V                |

| Logic low (logic threshold)                                  | $V_{\text{LGC}\_\text{LOW}}$ |                                                               |       |       | 0.8   | V                |

| DM pull-down resistor                                        |                              |                                                               |       | 19    |       | KΩ               |

| Logic I/O Characteristics                                    |                              |                                                               |       |       |       |                  |

| Low-logic voltage threshold                                  | VL                           |                                                               |       |       | 0.4   | V                |

| High-logic voltage threshold                                 | V <sub>H</sub>               |                                                               | 1.3   |       |       | V                |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN} = 5.0V$ , RS1 = 10m $\Omega$ , T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                 | Symbol         | Condition                     | Min  | Тур  | Max  | Units |

|-------------------------------------------|----------------|-------------------------------|------|------|------|-------|

| Output DP2/DM2 USB Signaling              |                | •                             |      |      | •    |       |

| BC1.2 DCP Mode                            |                |                               |      |      |      |       |

| DP2 and DM2 short resistance              |                | $V_{DP} = 0.8V, I_{DM} = 1mA$ |      | 158  | 200  | Ω     |

| BC1.2 SDP Mode                            |                |                               |      |      | •    |       |

| DP2 pull-down resistance                  |                |                               | 11   | 15   | 19   | kΩ    |

| DM2 pull-down resistance                  |                |                               | 11   | 15   | 19   | kΩ    |

| Divider Mode                              |                |                               |      |      |      | •     |

| DP2 output voltage                        |                | V <sub>OUT</sub> = 5V         | 2.6  | 2.7  | 2.8  | V     |

| DM2 output voltage                        |                | V <sub>OUT</sub> = 5V         | 2.6  | 2.7  | 2.8  | V     |

| DP2/DM2 output impedance                  |                |                               | 26   | 31   | 36   | kΩ    |

| 1.2V/1.2V Mode                            |                |                               |      |      |      |       |

| DP2/DM2 output voltage                    |                | $V_{OUT} = 5V$                | 1.21 | 1.26 | 1.31 | V     |

| DP2/DM2 output impedance                  |                |                               | 60   | 78   | 90   | kΩ    |

| Voltage-Based Fuel Gauge (VOREC           | ₃ = 4.2V, Cha  | rge Mode)                     |      |      |      |       |

| First level of battery voltage threshold  |                |                               | 3.52 | 3.6  | 3.69 | V     |

| Hysteresis                                |                |                               |      | 500  |      | mV    |

| Second level of battery voltage threshold |                |                               | 3.7  | 3.8  | 3.91 | V     |

| Hysteresis                                |                |                               |      | 500  |      | mV    |

| Third level of battery voltage threshold  |                |                               | 3.92 | 4.0  | 4.11 | V     |

| Hysteresis                                |                |                               |      | 500  |      | mV    |

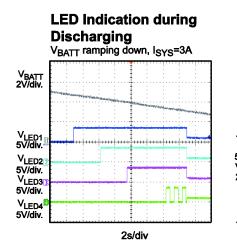

| Voltage-Based Fuel Gauge (VOREC           | ₃ = 4.2V, Disc | charge Mode)                  |      |      |      |       |

| First level of battery voltage threshold  |                |                               | 3.4  | 3.47 | 3.54 | V     |

| Hysteresis                                |                |                               |      | 500  |      | mV    |

| Second level of battery voltage threshold |                |                               | 3.55 | 3.62 | 3.69 | V     |

| Hysteresis                                |                |                               |      | 500  |      | mV    |

| Third level of battery voltage threshold  |                |                               | 3.7  | 3.77 | 3.84 | V     |

| Hysteresis                                |                |                               |      | 500  |      | mV    |

| Fourth level of battery voltage threshold |                |                               | 3.85 | 3.92 | 3.99 | V     |

| Hysteresis                                |                |                               |      | 500  |      | mV    |

NOTE:

5) Guaranteed by design.

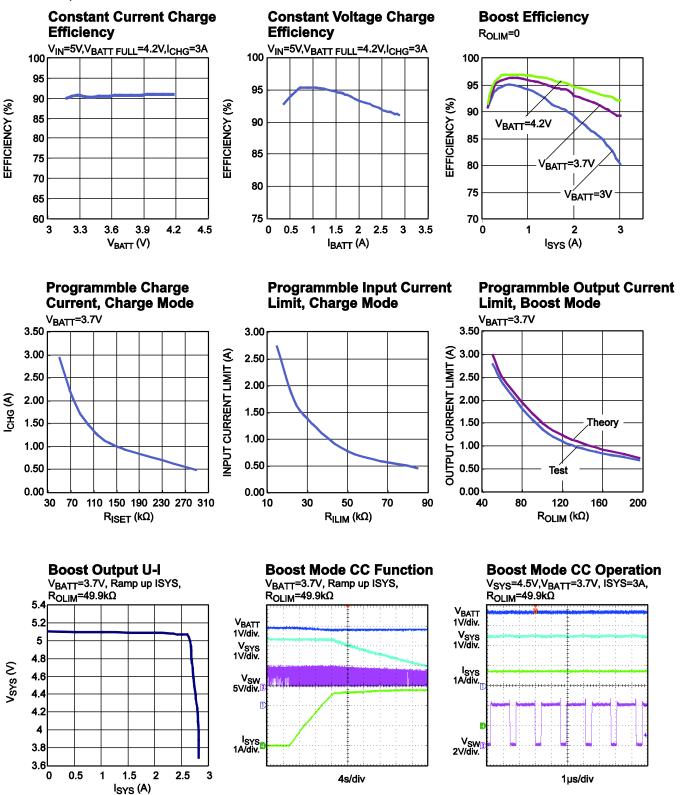

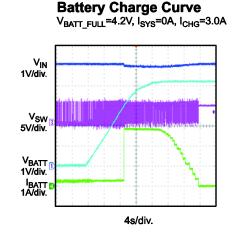

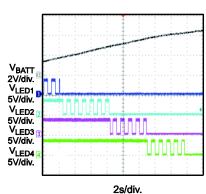

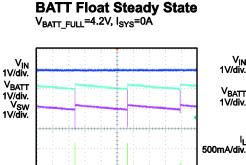

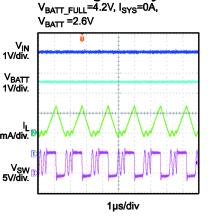

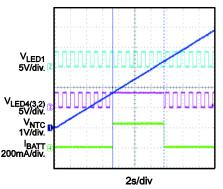

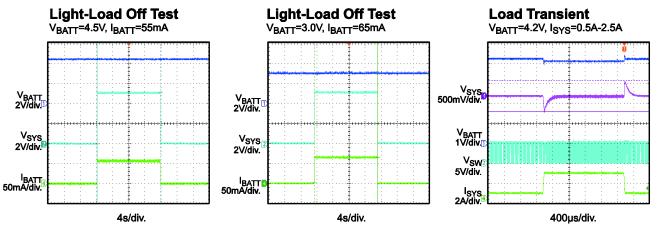

# TYPICAL PERFORMANCE CHARACTERISTICS

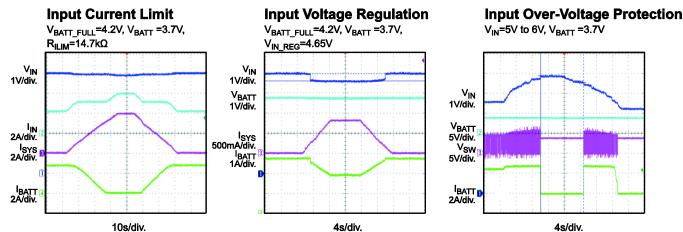

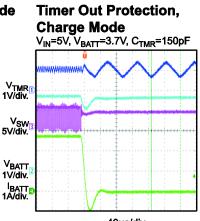

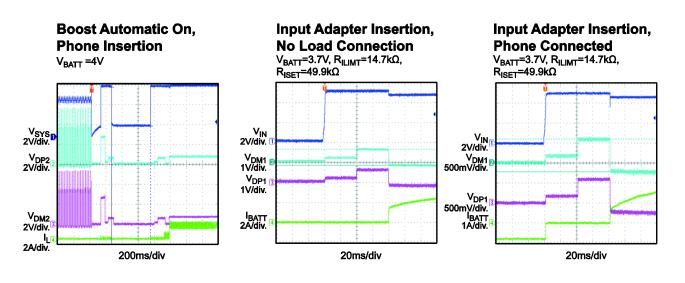

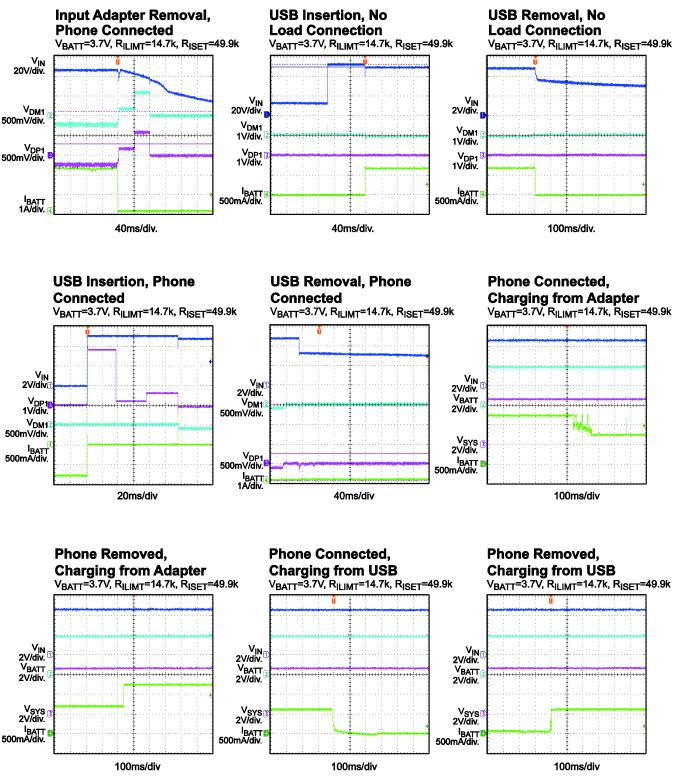

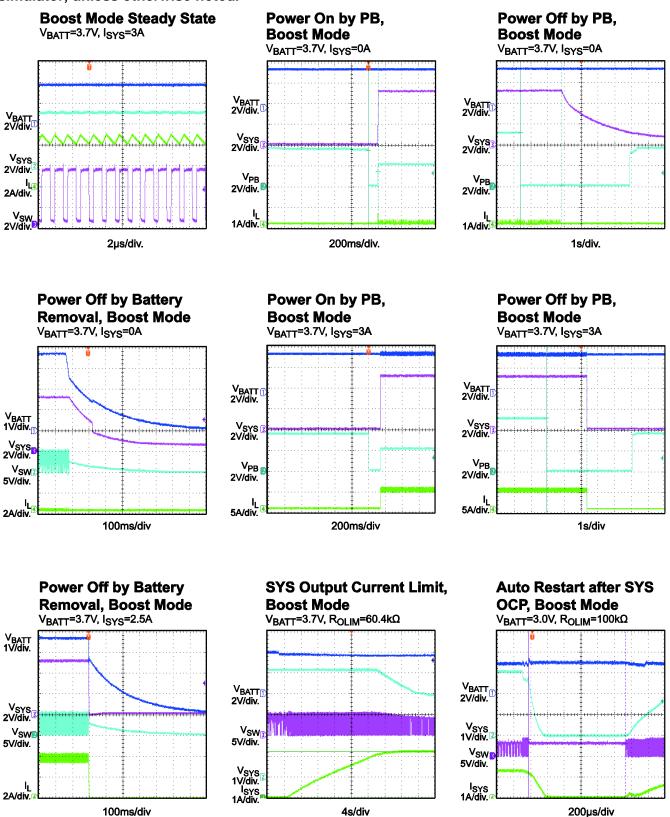

$V_{IN} = 5V$ ,  $C_{IN} = C_{BATT} = C_{SYS} = C2 = 22\mu$ F, L1 = 2.2 $\mu$ H, RS1 = 10m $\Omega$ , C4 =  $C_{TMR} = 0.1\mu$ F, battery simulator, unless otherwise noted.

MP2632 Rev.1.0 6/24/2016 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

VIN

1V/div. V<sub>BATT</sub> 5V/div.

V<sub>SW</sub> 1V/div.

IBATT

$V_{IN} = 5V$ ,  $C_{IN} = C_{BATT} = C_{SYS} = C2 = 22\mu$ F,  $L1 = 2.2\mu$ H,  $RS1 = 10m\Omega$ ,  $C4 = C_{TMR} = 0.1\mu$ F, battery simulator, unless otherwise noted.

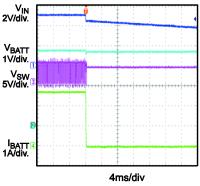

Auto-Recharge V<sub>BATT\_FULL</sub>=4.2V, I<sub>SYS</sub>=0A, I<sub>CHG</sub>=3.0A

2s/div.

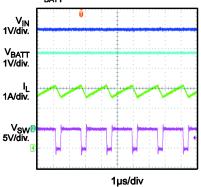

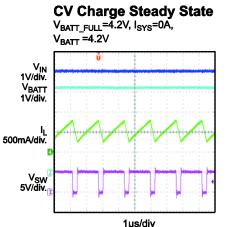

**TC Charge Steady State**

Indication during Charging  $V_{BATT_FULL}$ =4.2V,  $I_{SYS}$ =0A,  $I_{CHG}$ =3.0A

40ms/div

**CC Charge Steady State**

V<sub>BATT\_FULL</sub>=4.2V, I<sub>SYS</sub>=0A, V<sub>BATT</sub> =3.7V

MP2632 Rev.1.0 6/24/2016

ا ا.100mA/div

$V_{IN} = 5V$ ,  $C_{IN} = C_{BATT} = C_{SYS} = C2 = 22\mu$ F,  $L1 = 2.2\mu$ H,  $RS1 = 10m\Omega$ ,  $C4 = C_{TMR} = 0.1\mu$ F, battery simulator, unless otherwise noted.

Input Over-Current Protection  $V_{IN}$ =5V, Ramp up I<sub>SYS</sub> to 4.2A,  $V_{BATT}$ =3.7V

NTC Protection, Charge Mode  $V_{IN}$ =5V,  $V_{BATT}$ =2.6V

40µs/div

MP2632 Rev.1.0 6/24/2016 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

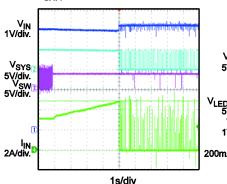

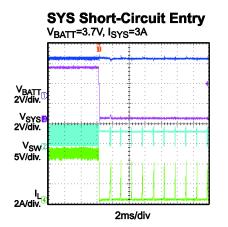

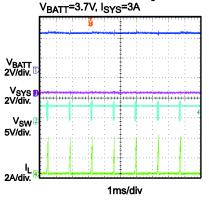

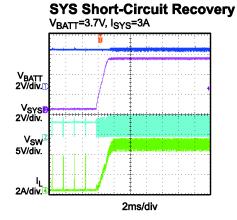

$V_{IN} = 5V$ ,  $C_{IN} = C_{BATT} = C_{SYS} = C2 = 22\mu$ F, L1 = 2.2 $\mu$ H, RS1 = 10m $\Omega$ , C4 =  $C_{TMR} = 0.1\mu$ F, battery simulator, unless otherwise noted.

$V_{IN} = 5V, C_{IN} = C_{BATT} = C_{SYS} = C2 = 22\mu F, L1 = 2.2\mu H, RS1 = 10m\Omega, C4 = C_{TMR} = 0.1\mu F, battery$ simulator, unless otherwise noted.

www.MonolithicPower.com

MP2632 Rev.1.0 6/24/2016

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

$V_{IN} = 5V$ ,  $C_{IN} = C_{BATT} = C_{SYS} = C2 = 22\mu$ F,  $L1 = 2.2\mu$ H,  $RS1 = 10m\Omega$ ,  $C4 = C_{TMR} = 0.1\mu$ F, battery simulator, unless otherwise noted.

SYS Short Steady

Torch Light

# **PIN FUNCTIONS**

| P/N  | Name | I/O   | Description                                                                                                                                                                                                                                                                                                     |

|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PGND | Power | Power ground.                                                                                                                                                                                                                                                                                                   |

| 2    | SW   | Power | <b>Switch output node.</b> It is not recommended to place vias on the SW plane during PCB layout.                                                                                                                                                                                                               |

| 3, 4 | SYS  | Power | <b>System output.</b> Place a ceramic capacitor of at least $22\mu$ F as close to SYS and PGND as possible. The total capacitance should not be lower than $44\mu$ F.                                                                                                                                           |

| 5    | VIN  | Power | Adapter input. Place a bypass capacitor close to VIN to prevent large input voltage spikes.                                                                                                                                                                                                                     |

| 6    | DM1  | Ι     | <b>Negative line of the input USB data line pair.</b> DM1 together with DP1 achieves the USB host. DM1 has automatic charging port detection.                                                                                                                                                                   |

| 7    | DP1  | I     | <b>Positive line of the input USB data line pair.</b> DP1 together with DM1 achieves the USB host. DP1 has automatic charging port detection.                                                                                                                                                                   |

| 8    | тс   | 0     | <b>Torch control output.</b> TC is the open-drain structure. The internal driver MOSFET is on when PB is pulled low for more than 1.5ms twice within one second.                                                                                                                                                |

| 9    | ILIM | I     | <b>Input current setting.</b> Connect ILIM to GND with an external resistor to program an input current limit in charge mode when a dedicated charger is detected.                                                                                                                                              |

| 10   | DM2  | 0     | <b>Negative line of the output USB data line pair.</b> DM2 together with DP2 automatically provides the correct voltage signal for attached portable equipment to perform DCP detection.                                                                                                                        |

| 11   | DP2  | 0     | <b>Positive line of the output USB data line pair.</b> DP2 together with DM2 automatically provides the correct voltage signal for attached portable equipment to perform DCP detection.                                                                                                                        |

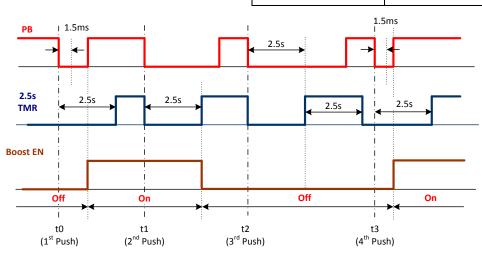

|      |      |       | <b>Push button input.</b> Connect a push button from PB to AGND. PB is pulled up by a resistor internally. When PB is set from high to low for more than 1.5ms, the boost is enabled and latched if $V_{IN}$ is not available.                                                                                  |

|      |      |       | LED1-4 are on for five seconds whenever PB is set from high to low for more than 1.5ms.                                                                                                                                                                                                                         |

| 12   | PB   | Ι     | If PB is set from high to low for more than 1.5ms twice within one second and the torch light is off, the torch light drive MOSFET is on and latched. However, if PB is set from high to low for more than 1.5ms twice within one second and the torch drive MOSFET is on, the torch light drive MOSFET is off. |

|      |      |       | If PB is set from high to low for more than 2.5 seconds, this is defined as a long push, and boost is shut down manually.                                                                                                                                                                                       |

| 13   | TMR  | I     | <b>Oscillator period timer.</b> Connect a timing capacitor between TMR and GND to set the oscillator period. Short TMR to GND to disable the timer function.                                                                                                                                                    |

| 14   | ISET | I     | <b>Programmable charge current.</b> Connect an external resistor to GND to program the charge current.                                                                                                                                                                                                          |

| 15   | OLIM | I     | <b>Programmable output current limit for boost mode.</b> Connect an external resistor to GND to program the system current in boost mode.                                                                                                                                                                       |

| P/N | Name | I/O | Description                                                                                                                                                                                                                         |

|-----|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | VCC  | I   | <b>Internal circuit power supply.</b> Bypass VCC to GND with a ceramic capacitor no higher than 100nF.                                                                                                                              |

| 17  | AGND | I/O | Analog ground.                                                                                                                                                                                                                      |

| 18  | VNTC | 0   | <b>Pull-up voltage source for the NTC function.</b> VNTC is connected to VCC through an internal MOSFET. VNTC is disconnected from VCC during sleep mode. VNTC should be the pull-up voltage of the external NTC resistive divider. |

| 19  | NTC  | I   | Negative temperature coefficient (NTC) thermistor.                                                                                                                                                                                  |

| 20  | VB   | I   | <b>Programmable battery full voltage.</b> Leave VB floating for 4.2V. Connect VB to logic high for 4.45V. Connect VB to GND for 4.35V.                                                                                              |

| 21  | BATT | Ι   | Positive battery terminal/battery charge current sense negative input.                                                                                                                                                              |

| 22  | CSP  | Ι   | Battery charge current sense positive input.                                                                                                                                                                                        |

| 23  | LED4 | 0   | LED4 together with LED1, LED2, and LED3 achieves the voltage-based fuel gauge indication.                                                                                                                                           |

| 24  | LED3 | 0   | LED3 together with LED1, LED2, and LED4 achieves the voltage-based fuel gauge indication.                                                                                                                                           |

| 25  | LED2 | 0   | LED2 together with LED1, LED3, and LED4 achieves the voltage-based fuel gauge indication.                                                                                                                                           |

| 26  | LED1 | 0   | LED1 together with LED2, LED3, and LED4 achieves the voltage-based fuel gauge indication.                                                                                                                                           |

# PIN FUNCTIONS (continued)

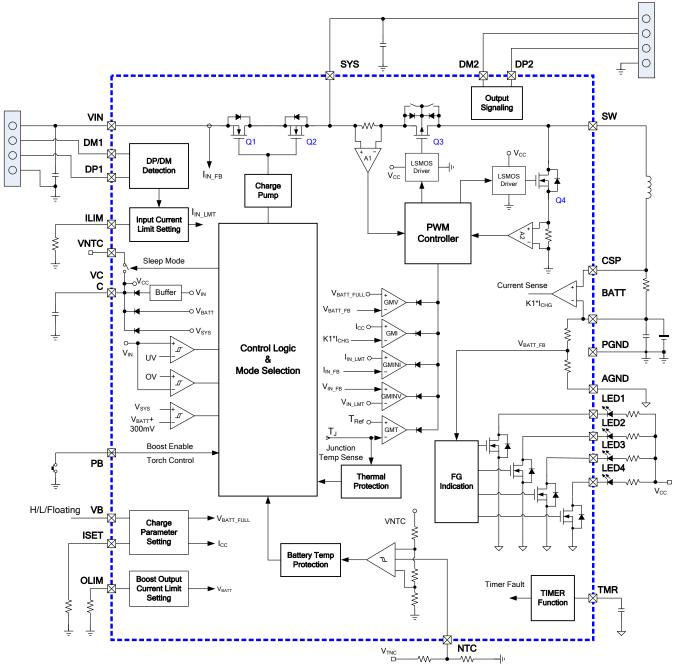

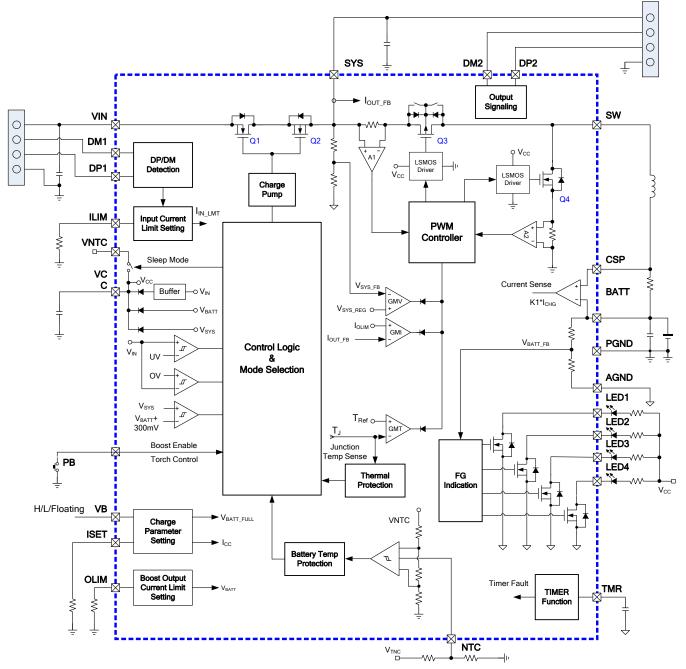

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram in Charge Mode

## **BLOCK DIAGRAM** (continued)

Figure 2: Functional Block Diagram in Boost Mode

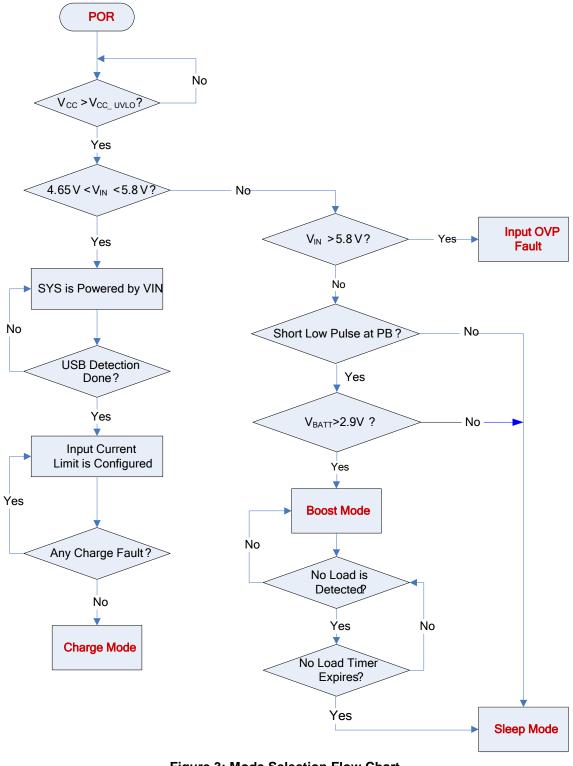

# **OPERATION FLOW CHART**

Figure 3: Mode Selection Flow Chart

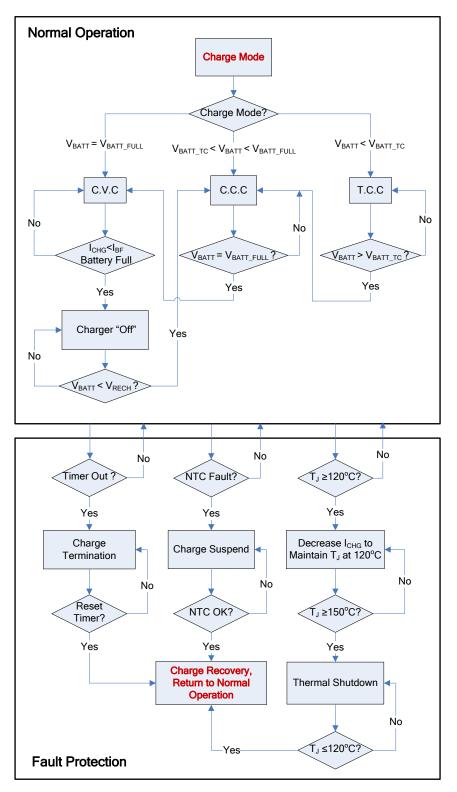

# **OPERATION FLOW CHART** (continued)

# **OPERATION FLOW CHART** (continued)

## **OPERATION FLOW CHART** (continued)

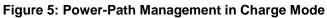

Figure 6: Operation Flow Chart in Boost Mode

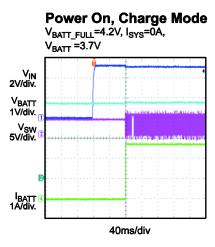

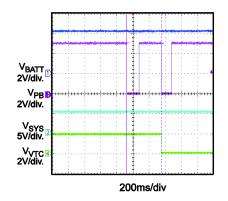

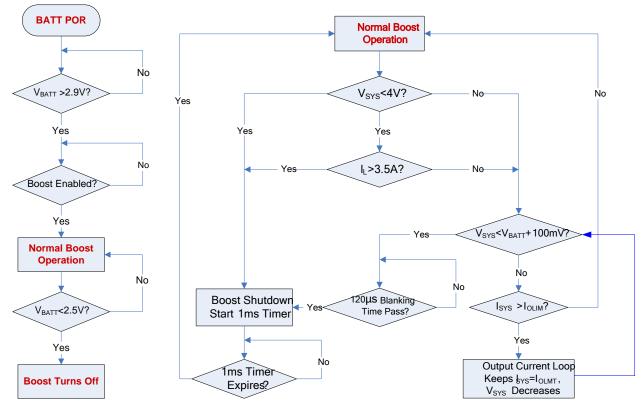

# START-UP TIME FLOW IN CHARGE MODE

Condition:  $V_{IN} = 5V$ ,  $V_{BATT} = 3.8V$

Figure 7: Input Power Start-Up Time Flow in Charge Mode

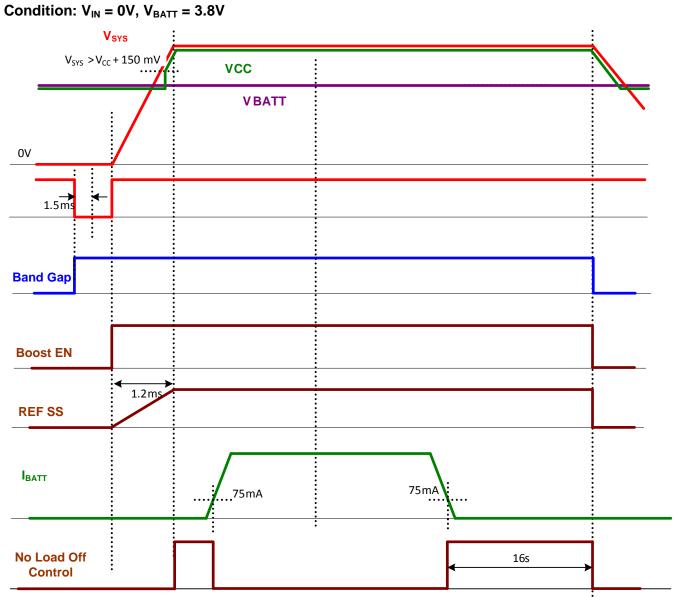

# START-UP TIME FLOW IN BOOST MODE

Figure 8: Boost Start-Up Time Flow in Boost Mode

# **OPERATION**

The MP2632 is a highly integrated, flexible, switch-mode battery charger with system powerpath management designed for single-cell Li-ion or Li-polymer battery use in a wide range of applications. Depending on the status of the input, the IC can operate in three different modes: charge mode, boost mode, and sleep mode.

In charge mode, the IC can work with a single-cell Liion or Li-polymer battery. In boost mode, the IC boosts the battery voltage to  $V_{SYS}$  to power higher voltage system rails. In sleep mode, both charging and boost operations are disabled, and the device enters a power saving mode to help reduce overall power consumption. The IC monitors  $V_{IN}$  to allow smooth transitions between different modes of operation.

#### **VCC Power Supply**

The MP2632 has an external VCC power supply. VCC is powered by the highest voltage level out of  $V_{SYS}$ ,  $V_{BATT}$ , and  $V_{IN}$  - 0.7V. An external capacitor is required to bypass VCC to GND. When VCC is higher than 2.2V, the internal control circuit is activated.

#### **Charge Mode Operation**

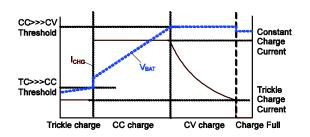

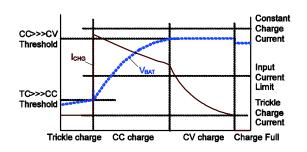

#### Charge Cycle (Trickle Charge $\rightarrow$ CC Charge $\rightarrow$ CV Charge)

In charge mode, the IC uses five control loops to regulate the input current, input voltage, charge current, charge voltage, and device junction temperature. The IC charges the battery in three phases: trickle current (TC), constant current (CC), and constant voltage (CV).

When charge operation is enabled, all five loops are active, but only one dictates the IC behavior. A typical battery charge profile is shown in Figure 9a. The charger stays in TC charge mode until the battery voltage reaches a TC-to-CC threshold. Otherwise, the charger enters CC charge mode.

When the battery voltage rises to the CV mode threshold, the charger operates in constant voltage mode. Figure 9b shows a typical charge profile when the input current limit loop dominates during the CC charge mode. In this case, the charger maximizes the charging current due to the switching-mode charging solution, resulting in charging that is faster than a traditional linear charging solution.

a) Without input current limit

b) With input current limit Figure 9: Typical Battery Charge Profile

### Auto-Recharge

Once the battery charge cycle is completed, the charger remains off. During this time, the system load may consume battery power, or the battery may self-discharge. To ensure that the battery does not go into depletion, a new charge cycle begins automatically when the battery voltage falls below the auto-recharge threshold and the input power is present. The timer resets when the auto-recharge cycle begins.

If the input power restarts during the off-state after the battery is fully charged, the charge cycle starts and the timer resets regardless of what the battery voltage is.

## **Charge Current Setting**

The external sense resistors (RS1 and  $R_{ISET}$ ) program the battery charge current ( $I_{CHG}$ ). Select  $R_{ISET}$  based on RS1.

To optimize the transfer efficiency, RS1 is recommended to be  $10m\Omega$ . The relationship between the R<sub>ISET</sub> and I<sub>CHG</sub> is shown in Equation (1):

$$I_{CHG}(A) = \frac{1500}{R_{ISET}(k\Omega) \times RS1(m\Omega)}$$

(1)

### **Battery Over-Voltage Protection (OVP)**

The IC has battery over-voltage protection (OVP). If the battery voltage exceeds the battery over-voltage threshold (103.5% of the battery's full voltage), charging is disabled. Under this condition, an internal  $5k\Omega$  dummy load draws a small current from BATT to reduce the battery voltage and protect the battery.

#### **Timer Operation in Charge Mode**

The IC uses an internal timer to terminate the charging. The timer remains active during the charging process. An external capacitor between TMR and GND programs the charge cycle duration.

If charging remains in TC mode beyond the trickle-charge time ( $T_{TRICKLE_TMR}$ ), charging is terminated. For the MP2632, the charge current in TC mode is fixed at 265mA, and the sense resistor (RS1) is set to 10m $\Omega$ . The length of the trickle-charge period can be determined with Equation (2):

$$\tau_{\text{TRICKLE}_\text{TMR}} = 17 \text{mins} \times \frac{C_{\text{TMR}}(\mu F)}{0.1 \mu F}$$

(2)

The maximum total charge time can be calculated with Equation (3):

$$\tau_{\text{TOTAL}_{\text{TMR}}} = 7.55 Hours \times \frac{C_{\text{TMR}}(\mu F)}{0.1 \mu F} \times \frac{1A}{I_{\text{CHG}}(A) + 0.1} \quad \textbf{(3)}$$

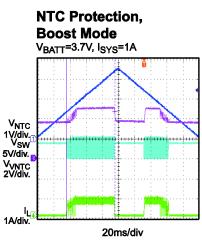

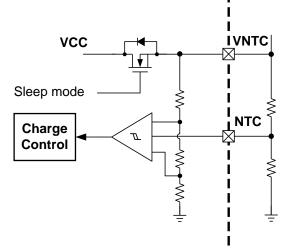

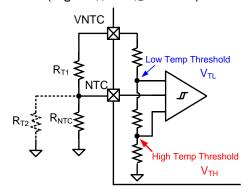

#### Negative Temperature Coefficient (NTC) Input for Battery Temperature Monitoring

The IC has a built-in NTC resistance window comparator, which allows the IC to monitor the battery temperature via the battery-integrated thermistor during both charge and boost modes. Connect an appropriate resistor from VNTC to NTC and connect the thermistor from NTC to GND. The resistor divider determines the NTC voltage depending on the battery temperature. If the NTC voltage falls outside of the NTC window, the IC stops charging. The operation then restarts if the temperature goes back into the NTC window range. Please refer to the Application Information section on page 33 for the appropriate resistor selection.

### **VNTC Power Supply**

The MP2632 has NTC protection in both boost mode and charge mode. To allow NTC protection in both boost mode and charge mode and to minimize the battery leakage current in sleep mode, the MP2632 uses a dedicated power supply pin for the pull-up voltage for the NTC protection function block. In boost mode and charge mode, VNTC is connected to VCC internally by a switch. In sleep mode, VNTC is disconnected from VCC to minimize the battery leakage current (see Figure 10).

Figure 10: NTC Protection Block

# Input DP1/DM1 USB Detection and Input Current Limit

Power devices (PDs) are able to draw current from the USB ports in personal computers to charge their batteries. If the portable device is attached to a USB host of the hub, then the USB specification requires the portable device to draw a limited current (usually 500mA). When the device is attached to a charging port, it is allowed to draw more than 1.5A.

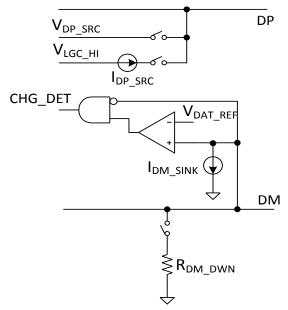

The IC features input source detection to determine the input current limit according to the input source (USB or adapter) (see Figure 11).

Figure 11: USB Port Detection

When the input source plugs in, the IC starts DP1/DM1 detection. DP1/DM1 detection has two steps: data contact detection (DCD) and primary detection. DCD uses a current source to detect when the data pins have made contact during an attach event. The protocol for data contact detection is as follows:

- The power device (PD) detects if V<sub>BUS</sub> is asserted.

- The PD turns on DP I<sub>DP\_SRC</sub> and the DM pulldown resistor for 40ms.

- The PD waits for the DP line to be low.

- The PD turns off I<sub>DP\_SRC</sub> and the DM pulldown resistor when the DP line is detected to be low, or when the 40ms timer expires.

DCD allows the PD to start primary detection once the data pins have made contact. Once the data contact is detected, the IC jumps to the primary detection immediately. If the data contact is not detected, the IC jumps to the primary detection automatically after 300ms from the beginning of the DCD.

Primary detection is used to distinguish between the USB host (or SDP) and different types of charging ports. During primary detection, the PD turns on  $V_{DP\_SRC}$  on DP1 and  $I_{DM\_SINK}$  on DM1. If the portable device is attached to a USB host, DM1 is low. If the power device is attached to CDP, DCP, or another dedicated charging port, DM1 remains high.

To be compatible with different capacities of the input source, the input current limit is recommended to be set using Table 2 if a 5V input is requested.

| DP1/DM1 Detection | I <sub>IN_LMT</sub>           |

|-------------------|-------------------------------|

| Floating          | 500mA                         |

| SDP               | 500mA                         |

| CDP or DCP        | Set through R <sub>ILIM</sub> |

The USB detection runs once  $V_{IN}$  is detected and is independent of the charge enable status. After the DP1/DM1 detection is done, the IC sets the input current limit as shown in Table 2.

When the detection algorithm is completed, the DP1 and DM1 signal lines enter a high-Z state with approximately 4pF of capacitive load.

# **External Input Current Limit Setting**

The IC has a dedicated pin used to program the input current limit when CDP or DCP is detected. The current at ILIM is a fraction of the input current. The ILIM voltage indicates the average input current of the switching regulator as determined by the resistor value between ILIM and GND. As the input current approaches the programmed input current limit, the charge current is reduced to give priority to the system power.

The input current limit threshold can be determined with Equation (4):

$$I_{\rm ILIM} = \frac{40(k\Omega)}{R_{\rm ILIM}(k\Omega)}(A)$$

(4)

# Input Voltage Regulation in Charge Mode

In charge mode, if the input power source is not sufficient for supporting both the charge current and the system load current, the input voltage decreases. As the input voltage internally approaches the 4.65V input voltage regulation threshold preset, the charge current is reduced to

give priority to the system power and maintain proper regulation of the input voltage.

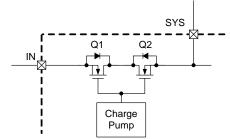

### Integrated Over-Current Protection and Over-Voltage Protection for Pass-Through Path

The IC has an integrated IN-to-SYS pass-through path to allow direct connection of the input voltage to the system. Therefore, the IC monitors both the input current and voltage continuously. In the event of an overload, the charge current is reduced to ensure priority of the system power requirements.

The IC also features input over-current and overvoltage protection for the IN-to-SYS pass-through path.

#### Input Over-Current Protection (OCP)

When the total input current exceeds 5A, Q2 is controlled linearly to regulate the current (see Figure 12). If the current continues to exceed 5A after 200µs of blanking time, Q2 is turned off. In the event of the input current exceeding 7A, Q2 is turned off almost instantaneously and without any blanking time. This is done to protect both Q1 and Q2.

#### Input Over-Voltage Protection (OVP)

The IC has a built-in over-voltage threshold  $(V_{IN_OVP})$ . When the input voltage is higher than  $V_{IN_OVP}$ , an invalid input power source is detected by the IC. At this time, the IN-to-SYS pass-through path is turned off to prevent connecting to the wrong adapter.

Figure 12: Integrated Pass-Through Path

# **Battery Short Protection**

In charge mode, the MP2632 uses two inherent current-limit thresholds due to a peak-currentcontrol strategy. CC and CV modes have a peakcurrent-limit threshold of 7A, while TC mode has a current-limit threshold of 4A. Therefore, the current limit threshold decreases to 4A when the battery voltage drops below the TC threshold. The switching frequency also decreases when the BATT voltage drops to 40% of the charge-full voltage.

## **Thermal Foldback Function**

The IC implements thermal protection to prevent thermal damage to the IC and the surrounding components. An internal thermal sense and feedback loop decreases the programmed charge current automatically when the die temperature reaches 120°C. This function is called the charge-current-thermal foldback. This function protects against thermal damage and sets the charge current based on requirements, rather than worst-case conditions while ensuring safe operation. The part also includes thermal shutdown protection, where the charging process is stopped if the junction temperature rises to 150°C.

## **Non-Sync Operation Mode**

During charging mode, the IC monitors the total input current flowing from IN to SYS continuously. When the input current is lower than 170mA, the low-side switch operates as a non-synchronous MOSFET.

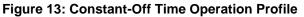

# Constant Off-Time Control for Large Duty Charging Operation

The IC has a built-in 600kHz frequency oscillator for the switching frequency. Unlike a traditional fixed-frequency peak-current control, the IC features a constant-off time control to support a constant current charge, even when the input voltage is very close to the battery voltage. The IC compares the high-side MOSFET sense current with the comp level continuously (see Figure 13). If the sense current does not reach the comp level within the original switching period, the next clock is delayed until the sense current reaches the comp level. As a result, the duty cycle is able to be extended as long as possible.

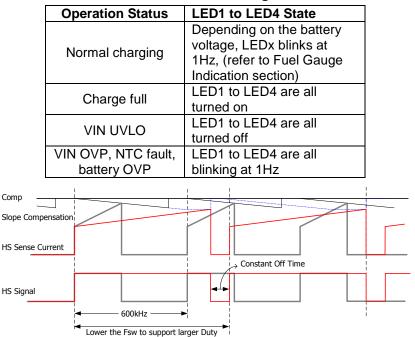

# Indication for Fault Flag in Charge Mode

The MP2632 is designed with distinct indication separating the charging fault from the normal operation. At the charging fault, including INOVP, BOVP, and NTC fault, the four LED pins blink with a 1Hz frequency simultaneously (see Table 3).

**Table 3: Indication at Charge Mode**

# Boost Mode Operation Low-Voltage Start-Up

The minimum battery voltage required to start up the circuit in boost mode is 2.9V. Initially, when  $V_{SYS}$  is less than  $V_{BATT}$ , the IC works in down mode. In this mode, the synchronous P-FET stops switching and its gate connects to  $V_{BATT}$ statically. The P-FET stays off for as long as the voltage across the parasitic  $C_{DS}$  ( $V_{SW}$ ) is lower than  $V_{BATT}$ . When the voltage across  $C_{DS}$ exceeds  $V_{BATT}$ , the synchronous P-FET enters linear mode, allowing the inductor current to decrease and flow into SYS. Once  $V_{SYS}$  exceeds  $V_{BATT}$ , the P-FET gate is released, and normal closed-loop PWM operation is initiated. In boost mode, the battery voltage can drop as low as 2.5V without affecting circuit operation.

# **SYS** Disconnect and Inrush Limiting

The IC can achieve true output disconnect by eliminating body diode conduction of the internal P-FET rectifier.  $V_{SYS}$  can go to 0V during shutdown, drawing no current from the input source. It also allows for inrush current limiting at start-up, minimizing surge currents from the input supply. To optimize the benefits of the output disconnect, avoid connecting an external Schottky diode between SW and SYS.

Board layout is extremely critical for minimizing voltage overshoot at SW due to stray inductance. Keep the output filter capacitor as close to SYS as possible, and use very low ESR/ESL ceramic capacitors tied to a good ground plane.

# **Boost Output Voltage Setting**

In boost mode, the IC programs the output voltage internally according to the load connected to SYS (5.1V or 5.2V) and provides built-in output over-voltage protection (OVP) to protect the device and other components against damage when  $V_{SYS}$  goes beyond 6V. Once output over-voltage occurs, the IC turns off the boost converter. When the voltage on  $V_{SYS}$  drops to a normal level, the boost converter restarts again when PB is set from high to low for more than 1.5ms.

# **Boost Output Current Limiting**

The IC integrates a programmable output current limit function in boost mode. If the boost output current exceeds this programmable limit, the output current is limited at this level and the SYS voltage begins to drop down. OLIM programs the current limit threshold up to 3.0A, per Equation (5):

$$I_{OLIM}(A) = \frac{1500}{R_{OLIM}(k\Omega) \times RS1(m\Omega)}$$

(5)

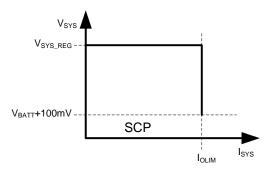

The MP2632 can operate in CC mode when the current limit is reached, and  $V_{IN}$  does not drop to the down mode threshold ( $V_{BATT}$  + 100mV) (see Figure 14).

Figure 14: Boost Output U-I Curve

The MP2632 not only has CC mode during the charging process, but also has CC mode operation in boost mode for various applications.

#### SYS to BATT Block Protection

When there is no  $V_{IN}$  and the boost mode is not on, the part is in sleep mode. The HS switch implements the body switch function, which connects the body diode of the switch to the high-voltage side of SW and SYS, which blocks the external voltage on SYS from flooding into the battery.

#### SYS Output Over-Current Protection (OCP)

The IC integrates a three-phase output overcurrent protection.

- <u>Phase one (boost mode output current limit)</u>: When the output current exceeds the programmed output current limit, the output constant current loop controls the output current, the output current remains at its limit (I<sub>OLIM</sub>), and V<sub>SYS</sub> decreases.

- <u>Phase two (down mode)</u>: When V<sub>SYS</sub> drops below V<sub>BATT</sub> + 100mV and the output current loop remains in control, the boost converter enters down mode and shuts down after 120µs of blanking time.

- <u>Phase three (short-circuit mode)</u>: When V<sub>SYS</sub> drops below 4.0V (2V during boost soft start), the boost converter shuts down immediately once the inductor current hits the foldback peak-current limit of the low-side N-FET. The boost converter can also recover automatically after a 1ms deglitch period.

### **Thermal Shutdown Protection**

The thermal shutdown protection is also active in boost mode. Once the junction temperature rises higher than 150°C, the IC enters thermal shutdown and does not resume normal operation until the junction temperature drops below 120°C.

## Automatic Off at Light Load

The boost turns off automatically if the load current at BATT is below the typical 75mA value for 16 seconds.

The MP2632 also features a long-push action on PB to shut down the boost manually. A low push on PB longer than 2.5 seconds is defined as a long push (see Figure 14 for PB action).

## Automatic Output DP2/DM2 Signaling

In boost mode, the IC sets the DP2/DM2 signal based on the load applied on USB2. In pass-through mode, DP2 and DM2 are set according to DP1/DM1 detection results.

In boost mode, DM2/DP2 are set based on three types of signals: DM2/DP2 separately biased with a 2.7V voltage signal (default), DM2/DP2 shorted, and DM2/DP2 shorted with a 1.2V bias.

In pass-through mode, DM2/DP2 are connected together if the dedicated charger ports are detected, and pulled down to ground separately with a  $15k\Omega$  resistor if SDP is identified.

## **Torch Control**

If the internal torch drive FET is off when PB is pulled from high to low for more than 1.5ms twice within one second, the drive FET is turned on. Conversely, if the torch drive FET is on, the drive FET is turned off.

Once the torch light is turned on, the automatic off function is blocked.

## **PB** Control

PB is used to control the enable of boost mode. Pull PB from high to low for more than 1.5ms to enable boost mode; pull PB from high to low for 2.5s to disable boost mode.

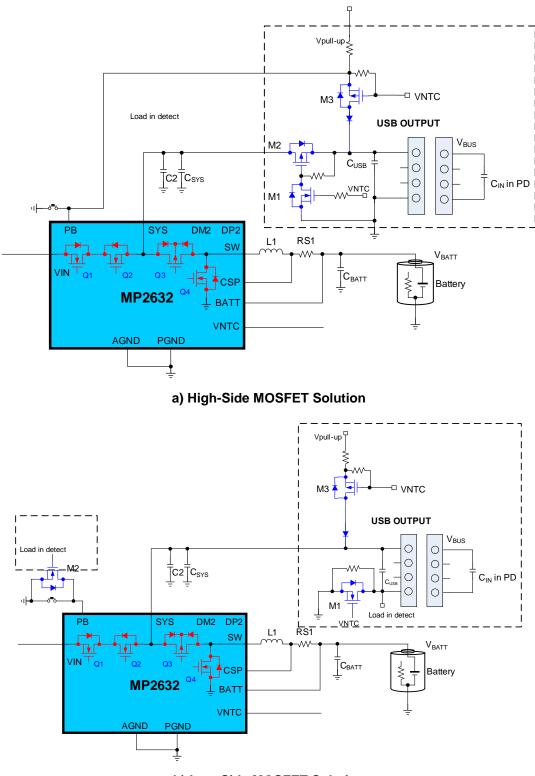

#### Automatic On when Load is Applied

The boost turns on automatically when PB is pulled from high to low for more than 1.5ms, or when the load is plugged in to USB2 using the PB control.

To detect the USB load plug-in, the RC network is connected to the USB port shield floating in the PCB. Once the USB load is inserted, the USB connector shield is grounded through the USB load. A short pulse (high to low for more than 1.5ms) is generated in PB, resulting in the start of boost.

An RC network can also be connected in  $V_{BUS}$  of the USB output port. During load insertion, the load input cap generates a high-to-low pulse for more than 1.5ms to start the boost (see Figure 15). The circuit in the dash frame is the automatic load detection circuit. M2 is used to decouple the USB port from the V<sub>SYS</sub> cap (C2, C<sub>SYS</sub>), and M1 is used to drive M2.

Once a phone is plugged in, the voltage at  $C_{\text{USB}}$  is pulled down because the input cap inside the phone is far larger than  $C_{\text{USB}}$ , so the falling edge is delivered to PB to enable boost automatically.

M3 is used to cut off PB to and from the USB port when boost is turned on. The PB state is not affected by the spec of the inserted load of the USB port. Choose M3 with a low turn-on threshold (-0.7V is recommended) which can ensure that it is fully on when the load is inserted and that its on resistance does not cause too much of a voltage drop.

# 4-LED Driver for Voltage-Based Fuel Gauge

The IC provides 4-LED drivers for a voltagebased fuel gauge. The driver is connected to an internal open-drain FET. The 4-LED indication values are shown in Table 4.

The LED threshold can be programmed using a fuse. Each threshold can be adjusted from 150mV to 200mV with 50mV steps from their default value.

The LED threshold is also adjusted automatically based on the  $V_{BAT_REG}$  setting. The  $V_{OREG}$  difference is considered to be offset for LED thresholds.

During the voltage measurement, the battery impedance  $(50m\Omega)$  should be compensated based on the battery current to get a precise battery voltage for fuel gauge indication.

#### Indication for Fault Flag in Boost Mode

To minimize the power consumption of the battery, the indication is active once PB is shortpushed in normal discharge operation, and turns off after five seconds automatically.

#### Table 4: Indication at Discharge Mode

| Operation status   | LED1 to LED4 state                                                                                      |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------|--|--|

|                    |                                                                                                         |  |  |

| Normal discharging | Depending on the battery<br>voltage, LEDx is turned off.<br>(refer to Fuel Gauge<br>Indication section) |  |  |

| NTC fault          | LED1 to LED4 are all blinking<br>at 1Hz                                                                 |  |  |

#### Figure 15: PB Action Profile

MP2632 Rev.1.0 6/24/2016

| Mode               | V <sub>BATT</sub>                         | SOC         | LED1  | LED2  | LED3  | LED4  |

|--------------------|-------------------------------------------|-------------|-------|-------|-------|-------|

|                    | V <sub>BATT</sub> < 3.6V                  | <25%        | Flash | Off   | Off   | Off   |

|                    | [3.6V, 3.8V)                              | [25%, 50%)  | On    | Flash | Off   | Off   |

| Charging           | [3.8V, 4.0V)                              | [50%, 75%)  | On    | On    | Flash | Off   |

|                    | CV mode, [4.0V, 4.2V),<br>not terminated  | [75%, 100%) | On    | On    | On    | Flash |

|                    | $V_{BATT} \ge 4.0$ , terminated           | 100%        | On    | On    | On    | On    |

|                    |                                           |             |       | -     |       | -     |

|                    | V <sub>BATT</sub> ≥ 3.92V                 | >75%        | On    | On    | On    | On    |

|                    | [3.77V, 3.92V)                            | [50%, 75%)  | On    | On    | On    | Off   |

| Discharging        | [3.62V, 3.77V)                            | [25%, 50%)  | On    | On    | Off   | Off   |

| (All off after 5s) | [3.47V, 3.62V)                            | [5%, 25%)   | On    | Off   | Off   | Off   |

|                    | [V <sub>BAT ULVO</sub> , 3.47V)           | [1%, 5%)    | Flash | Off   | Off   | Off   |

|                    | V <sub>BATT</sub> < V <sub>BAT_UVLO</sub> | <1%         | Off   | Off   | Off   | Off   |

#### **Table 5: Indication during Normal Operation**

## **APPLICATION INFORMATION**

# Setting the Charge Current in Charge Mode

In charge mode, both the external sense resistor (RS1) and the resistor ( $R_{ISET}$ ) connect to ISET to set the charge current ( $I_{CHG}$ ) of the MP2632 (see the Typical Application circuit on page 2). Given the expected  $I_{CHG}$  and RS1 values,  $R_{ISET}$  can be calculated with Equation (6):

$$I_{CHG}(A) = \frac{1500}{R_{ISET}(k\Omega) \times RS1(m\Omega)}$$

(6)

For example, if  $I_{CHG} = 3.0A$  and  $RS1 = 10m\Omega$ , then  $R_{ISET} = 49.9k\Omega$ .

Given a  $10m\Omega$  RS1, Table 6 lists the expected  $R_{ISET}$  values for the typical charge current.

Table 6: Charging Current vs. RISET

| R <sub>ISET</sub> (kΩ) | Charge Current (A) |

|------------------------|--------------------|

| 150                    | 1.0                |

| 100                    | 1.5                |

| 75                     | 2.0                |

| 60                     | 2.5                |

| 49.9                   | 3.0                |

# Setting the Input Current Limit in Charge Mode

In charge mode, connect a resistor from ILIM to AGND to program the input current limit if a dedicated charger (CDP or DCP) is detected. The relationship between the input current limit and setting resistor is shown in Equation (7):

$$I_{\rm ILIM} = \frac{40(k\Omega)}{R_{\rm ILIM}(k\Omega)}(A)$$

(7)

RILIM must exceed 14.7k $\Omega$  so that IIN\_LIM is in the range of 0A to 2.7A.

#### **NTC Function in Charge Mode**

An internal resistor divider sets the low temperature threshold ( $V_{TL}$ ) and high temperature threshold ( $V_{TH}$ ) at 66.6% of  $V_{SYS}$  and 35% of  $V_{SYS}$ , respectively (see Figure 16). For a given NTC thermistor, select an appropriate  $R_{T1}$  and  $R_{T2}$  to set the NTC window with Equation (8) and Equation (9):

$$\frac{V_{\text{TL}}}{V_{\text{SYS}}} = \frac{R_{\text{T2}} / / R_{\text{NTC}\_Cold}}{R_{\text{T1}} + R_{\text{T2}} / / R_{\text{NTC}\_Cold}} = TL = 66.6\% \quad (8)$$

$$\frac{V_{TH}}{V_{SYS}} = \frac{R_{T2} / / R_{NTC\_Hot}}{R_{T1} + R_{T2} / / R_{NTC\_Hot}} = TH = 35\%$$

(9)

Where  $R_{NTC\_Hot}$  is the value of the NTC resistor at the upper bound of its operating temperature range, and  $R_{NTC\_Cold}$  is its lower bound.

The two resistors  $R_{T1}$  and  $R_{T2}$  determine the upper and lower temperature limits independently. This flexibility allows the IC to operate with most NTC resistors for different temperature range requirements. Calculate  $R_{T1}$  and  $R_{T2}$  with Equation (10) and Equation (11):

$$R_{T1} = \frac{R_{\text{NTC\_Hot}} \times R_{\text{NTC\_Cold}} \times (TL - TH)}{TH \times TL \times (R_{\text{NTC\_Cold}} - R_{\text{NTC\_Hot}})}$$

(10)

$$R_{T2} = \frac{(TL - TH) \times R_{NTC\_Cold} \times R_{NTC\_Hot}}{(1 - TL) \times TH \times R_{NTC\_Cold} - (1 - TH) \times TL \times R_{NTC\_Hot}}$$

(11)

For example, the NCP18XH103 thermistor has the following electrical characteristics:

- At 0°C, R<sub>NTC\_Cold</sub> = 27.445kΩ

- At 50°C, R<sub>NTC\_Hot</sub> = 4.1601kΩ

Based on Equation (17) and Equation (18), an  $R_{T1}$  value of  $6.65k\Omega$  and an  $R_{T2}$  value of  $25.63k\Omega$  are suitable for an NTC window between 0°C and 50°C. Approximate values are  $R_{T1} = 6.65k\Omega$  and  $R_{T2} = 25.5k\Omega$ .

If no external NTC is available, connect  $R_{T1}$  and  $R_{T2}$  to keep the voltage on NTC within the valid NTC window (e.g.:  $R_{T1} = R_{T2} = 10k\Omega$ ).

Figure 16: NTC Function Block

For convenience, an NTC thermistor design spreadsheet has also been provided.

# Setting the Output Current Limit in Boost Mode

In boost mode, connect a resistor from OLIM to AGND to program the output current limit. The relationship between the output current limit and the setting resistor is shown in Equation (12):

$$I_{\text{OLIM}}(A) = \frac{1500}{R_{\text{OLIM}}(k\Omega) \times \text{RS1(m}\Omega)}$$

(12)

The output current limit of the boost can be programmed up to 3.0A.

Given a  $10m\Omega$  RS1, Table 7 lists the expected  $R_{OLIM}$  values for the typical output current limit.

Table 7: Output Current vs. ROLIM

| •                  |

|--------------------|

| Output Current (A) |

| 1.0                |

| 1.5                |

| 2.0                |

| 2.5                |

| 3.0                |

|                    |

### **Selecting the Inductor**

The inductor selection trades off between cost, size, and efficiency. A lower inductance value corresponds with a smaller size, but results in higher current ripples, higher magnetic hysteretic losses, and higher output capacitances. However, a higher inductance value benefits from lower ripple currents and smaller output filter capacitors, but results in a higher inductor DC resistance (DCR) loss. Choose an inductor that does not saturate under the worst-case load condition.

In charge mode, the MP2632 works as a buck converter. The required inductance can be estimated with Equation (13):

$$L = \frac{V_{IN} - V_{BATT}}{\Delta I_{L_{MAX}}} \times \frac{V_{BATT}}{V_{IN} \times f_{S}}$$

(13)

Where V<sub>IN</sub> is the typical input voltage, V<sub>BATT</sub> is the CC charge threshold,  $f_S$  is the switching frequency, and  $\Delta I_{L\_MAX}$  is the maximum peak-to-peak inductor current, which is usually designed at 30% - 40% of the CC charge current.

With a typical 5V input voltage, if there is a 35% inductor current ripple at the corner point between the trickle charge and the CC charge ( $V_{BATT} = 3V$ ,  $I_{CHG} = 2.5A$ ), then the inductance is 2.2µH.

In boost mode, the MP2637 works as a boost converter. The required inductance value can be calculated with Equation (14), Equation (15), and Equation (16):

$$L = \frac{V_{BATT} \times (V_{SYS} - V_{BATT})}{V_{SYS} \times f_{S} \times \Delta I_{L_{MAX}}}$$

(14)

$$\Delta I_{L_{MAX}} = (30\% - 40\%) \times I_{BATT(MAX)}$$

(15)

$$I_{\text{BATT}(\text{MAX})} = \frac{V_{\text{SYS}} \times I_{\text{SYS}(\text{MAX})}}{V_{\text{BATT}} \times \eta} \tag{16}$$

Where  $V_{BATT}$  is the minimum battery voltage,  $f_{SW}$  is the switching frequency, and  $\Delta I_{L_MAX}$  is the peak-to-peak inductor ripple current (approximately 30% of the maximum battery current ( $I_{BATT(MAX)}$ )),  $I_{SYS(MAX)}$  is the system current, and  $\eta$  is the efficiency.

The worst case occurs if the battery voltage is 3V, there is a 30% inductor current ripple, and the typical system voltage is  $V_{SYS} = 5V$ . Then, the inductance is 1.5µH when the efficiency is 90%.

For best results, use an inductor with an inductance of  $2.2\mu$ H with a DC current rating no lower than the peak current of the MOSFET. For higher efficiency, minimize the inductor's DC resistance.

## Selecting the Input Capacitor (CIN)

The input capacitor ( $C_{IN}$ ) reduces both the surge current drawn from the input and the switching noise from the device. The input capacitor impedance at the switching frequency should be less than the input source impedance to prevent the high-frequency switching current from passing to the input. Ceramic capacitors with X7R dielectrics are recommended because of their low ESR and small temperature coefficients. For most applications, a 22µF capacitor is sufficient.

# Selecting the System Capacitor (C<sub>SYS</sub>)

Select the system capacitor ( $C_{SYS}$ ) based on the demand of the system current ripple. In charge mode,  $C_{SYS}$  acts as the input capacitor of the buck converter. The input current ripple can be calculated with Equation (17):

$$I_{\text{RMS}_{\text{MAX}}} = I_{\text{SYS}_{\text{MAX}}} \times \frac{\sqrt{V_{\text{TC}} \times (V_{\text{IN}_{\text{MAX}}} - V_{\text{TC}})}}{V_{\text{IN}_{\text{MAX}}}} \quad (17)$$

In boost mode,  $C_{SYS}$  is the output capacitor of the boost converter.  $C_{SYS}$  keeps the system voltage ripple small and ensures feedback loop stability. The system current ripple can be calculated with Equation (18):

$$I_{\text{RMS}_{\text{MAX}}} = I_{\text{SYS}_{\text{MAX}}} \times \frac{\sqrt{V_{\text{TC}} \times (V_{\text{SYS}_{\text{MAX}}} - V_{\text{TC}})}}{V_{\text{SYS}_{\text{MAX}}}}$$

(18)

Since the input voltage is passed to the system directly,  $V_{IN\_MAX}$  is equal to  $V_{SYS\_MAX}$ , and both charge mode and boost mode have the same system current ripple.

When  $I_{CC\_MAX}$  equals 2A,  $V_{TC}$  equals 3V,  $V_{IN\_MAX}$  equals 6V, and the maximum ripple current is 1A. Select the system capacitors based on the ripplecurrent temperature rise, not exceeding 10°C. For best results, use low ESR ceramic capacitors with X7R dielectrics and small temperature coefficients. For most applications, use three 22µF capacitors.

# Selecting the Battery Capacitor (CBATT)

$C_{BATT}$  is in parallel with the battery to absorb the high-frequency switching ripple current. In charge mode, the capacitor ( $C_{BATT}$ ) is the output capacitor of the buck converter. The output voltage ripple is then calculated with Equation (19):

$$\Delta r_{BATT} = \frac{\Delta V_{BATT}}{V_{BATT}} = \frac{1 - V_{BATT} / V_{SYS}}{8 \times C_{BATT} \times f_{SW}^2 \times L}$$

(19)

In boost mode,  $C_{BATT}$  is the input capacitor of the boost converter. The input voltage ripple is the same as the output voltage ripple from Equation (19).

Both charge mode and boost mode have the same battery voltage ripple.  $C_{BATT}$  can be calculated with Equation (20):

$$C_{\text{BATT}} = \frac{1 - V_{\text{TC}} / V_{\text{SYS}_{\text{MAX}}}}{8 \times \Delta r_{\text{BATT}_{\text{MAX}}} \times f_{\text{SW}}^2 \times L}$$

(20)

To guarantee ±0.5% BATT voltage accuracy, the maximum BATT voltage ripple must not exceed 0.5% (e.g.: 0.1%). The worst case occurs at the minimum battery voltage of the CC charge with the maximum input voltage. For example,  $V_{SYS\_MAX} = 6V$ ,  $V_{CC\_MIN} = V_{TC} = 3V$ ,  $L = 2.2\mu$ H,  $f_S = 600$ kHz,  $\Delta r_{BATT\_MAX} = 0.1\%$ , and  $C_{BATT}$  is  $22\mu$ F.

A 22µF ceramic capacitor with X7R dielectrics is sufficient.

#### PCB Layout Guidelines

Efficient PCB layout is critical for meeting specified noise, efficiency, and stability requirements. The following design considerations can improve circuit performance:

- 1. Route the power stage adjacent to their grounds.

- 2. Minimize the high-side switching node (SW, inductor) trace lengths in the high-current paths.

- 3. Keep the switching node short and away from all small control signals, especially the feedback network.

- 4. Place the input capacitor as close to  $V_{IN}$  and PGND as possible.

- 5. Place the local power input capacitors connected from SYS to PGND as close to the IC as possible.

- 6. Place the output inductor close to the IC.

- 7. Connect the output capacitor between the inductor and PGND of the IC.

- 8. Connect the power pads for VIN, SYS, SW, BATT, and PGND to as many coppers planes on the board as possible for high-current applications.

This improves thermal performance because the board conducts heat away from the IC.

9. Connect a ground plane directly to the return of all components through vias (e.g.: two vias per capacitor for power-stage capacitors, and one via per capacitor for small-signal components).

A star ground design approach is typically used to keep circuit block currents isolated (power-signal/control-signal), which reduces noise-coupling and ground-bounce issues. A single ground plane for this design provides good results.

10. Place the ISET, OLIM, and ILIM resistors very close to their respective IC pins.

# **TYPICAL APPLICATION CIRCUITS**

b) Low-Side MOSFET Solution Figure 17: Load Detection Circuit

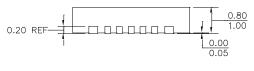

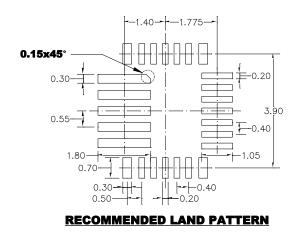

# **PACKAGE INFORMATION**

QFN-26 (4mmx4mm)

**BOTTOM VIEW**

#### NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS. 2) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX. 3) DRAWING CONFORMS TO JEDEC MO-220.

4) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.