#### DESCRIPTION

The MP6411 is a windowed watchdog timer. It is used to reset and monitor the microcontroller. In normal operation, the MCU sends a trigger signal to the MP6411 in a defined time window cyclically. A missing or fault trigger signal causes the watchdog to reset the MCU.

The MP6411 provides a reset signal (low-level voltage) to the MCU during power-up or under voltage.

By setting MODE to high or low, the watchdog operates in long window mode or short window mode; the window is programmable.

The MP6411 is available in SOIC8 package.

#### **FEATURES**

- Windowed Watchdog

- Power-On Reset during Power-Up and Under Voltage

- Programmable Short Window Mode or Long Window Mode

- Watchdog Disable Function

- Low Shutdown Mode Current

- SOIC8 Package

## **APPLICATIONS**

- Automotive Systems

- Industrial Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

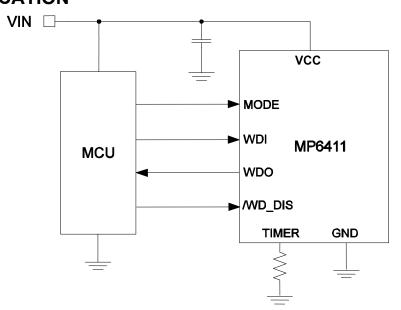

#### TYPICAL APPLICATION

# **ORDERING INFORMATION**

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| MP6411GS     | SOIC-8  | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP6411GS–Z);

## **TOP MARKING**

MP6411 LLLLLLL MPSYWW

MP6411: Product code of MP6411GS

LLLLLLL: Lot number MPS: MPS prefix Y: Year code WW: Week code

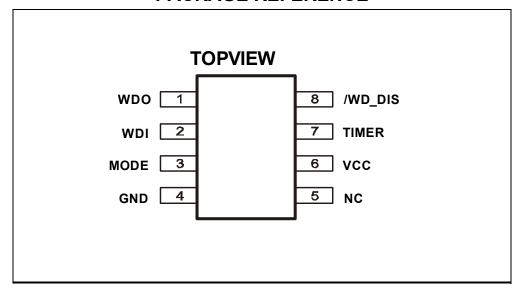

#### PACKAGE REFERENCE

##

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|------------------------|-------------------------|-------------------------|------|

| SOIC-8                 | 96                      | 45                      | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 5V,  $T_J$  = +25°C, unless otherwise noted.

| Parameter                                              | Symbol                | Condition                                 | Min                  | Тур  | Max  | Units |  |

|--------------------------------------------------------|-----------------------|-------------------------------------------|----------------------|------|------|-------|--|

| Power Supply                                           |                       |                                           |                      |      |      |       |  |

| Timer voltage                                          |                       | R <sub>TIMER</sub> = 51k                  |                      | 0.3  |      | V     |  |

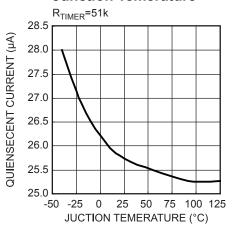

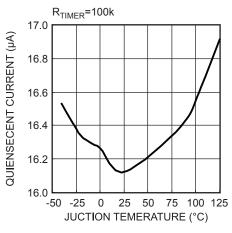

| Quiescent current                                      | ΙQ                    | R <sub>TIMER</sub> = 100k                 |                      | 16   | 19   | μΑ    |  |

|                                                        |                       | R <sub>TIMER</sub> = 51k                  |                      | 25   | 32   | μΑ    |  |

| Power on reset threshold                               | V <sub>POR-HIGH</sub> | WDO goes high with rising V <sub>CC</sub> | 4.4                  | 4.6  | 4.8  | ٧     |  |

|                                                        | $V_{POR-LOW}$         | WDO goes low with falling V <sub>CC</sub> | 4.3                  | 4.5  | 4.7  | V     |  |

| Timing                                                 | ı                     |                                           | ı                    |      | 1    | 1     |  |

| Single period                                          | Т                     | R <sub>TIMER</sub> = 51k                  | -10%                 | 880  | +10% | μs    |  |

| Power on delay <sup>(5)</sup>                          | t <sub>0</sub>        | R <sub>TIMER</sub> = 51k                  |                      | 10   |      | cycle |  |

| Sync signal monitoring time <sup>(5)</sup>             | t <sub>1</sub>        | R <sub>TIMER</sub> = 51k                  |                      | 450  |      | cycle |  |

| Watchdog window close time (short mode) <sup>(5)</sup> | t <sub>2</sub>        | R <sub>TIMER</sub> = 51k, mode = low      |                      | 15   |      | cycle |  |

| Watchdog window open time (short mode) (5)             | t <sub>3</sub>        | R <sub>TIMER</sub> = 51k, mode = low      |                      | 10   |      | cycle |  |

| Watchdog window close time (long mode) (5)             | t <sub>4</sub>        | R <sub>TIMER</sub> = 51k, mode = high     |                      | 1500 |      | cycle |  |

| Watchdog window open time (long mode) (5)              | t <sub>5</sub>        | R <sub>TIMER</sub> = 51k, mode = high     |                      | 1000 |      | cycle |  |

| WDO reset pulse width <sup>(5)</sup>                   | t <sub>6</sub>        | R <sub>TIMER</sub> = 51k                  |                      | 4    |      | cycle |  |

| WDI_OK pulse width                                     |                       |                                           | 10                   |      | 5000 | μs    |  |

| Input and Output                                       |                       |                                           |                      |      | •    |       |  |

| WDI logic high                                         |                       |                                           | 3.2                  |      |      | V     |  |

| WDI logic low                                          |                       |                                           |                      |      | 0.8  | V     |  |

| MODE logic high                                        |                       |                                           | 3.2                  |      |      | V     |  |

| MODE logic low                                         |                       |                                           |                      |      | 0.8  | V     |  |

| MODE input Current                                     |                       | MODE = 5V                                 |                      | 0.1  | 1    | μA    |  |

|                                                        |                       | MODE = 0V                                 |                      | 5    | 8    | μA    |  |

| /WD_DIS logic high                                     |                       |                                           | 3.2                  |      |      | V     |  |

| /WD_DIS logic low                                      |                       |                                           |                      |      | 0.8  | V     |  |

| /WD_DIS input Current                                  |                       | WD_DIS = 5V                               |                      | 0.1  | 1    | μA    |  |

|                                                        |                       | WD_DIS = 0V                               |                      | 5    | 8    | μA    |  |

| WDO high                                               |                       | VCC = 5V, I <sub>WDO</sub> = 1mA          | V <sub>CC</sub> -0.2 |      |      | V     |  |

| WDO low                                                |                       | VCC = 5V, I <sub>WDO</sub> = 1mA          |                      |      | 0.2  | V     |  |

|                                                        |                       | VCC = 1V, I <sub>WDO</sub> = 300μA        |                      |      | 0.1  | V     |  |

#### Notes:

5) Derived from bench characterization. Not tested in production.

#### TYPICAL CHARATERISTICS

**Quiescent Current vs. Junction Temerature**

**Quiescent Current vs. Junction Temerature**

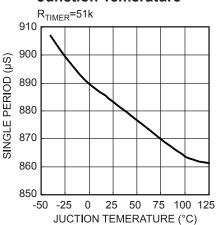

Single Period vs.

Junction Temerature

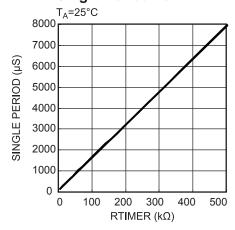

#### Single Period vs. RTIMER

# **PIN FUNCTION**

| Pin# | Name    | Description                                                                                                                                                                |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | WDO     | Watchdog output. WDO outputs a reset signal to the MCU.                                                                                                                    |

| 2    | WDI     | Watchdog input. WDI receives the trigger signal from the MCU.                                                                                                              |

| 3    | MODE    | Mode switching pin. Pull MODE high to make the watchdog operate in long window mode; pull MODE low to make it work in short window mode. MODE has a weak internal pull-up. |

| 4    | GND     | Ground.                                                                                                                                                                    |

| 5    | NC      | Not connected.                                                                                                                                                             |

| 6    | VCC     | Power input. A $0.1\mu\text{F}$ ceramic capacitor is recommended to put between VCC and GND pins.                                                                          |

| 7    | TIMER   | Watchdog timer pin. TIMER sets the time-out with an external resistor                                                                                                      |

| 8    | /WD_DIS | Watchdog disable pin. Pull /WD_DIS low to disable the watchdog; pull /WD_DIS high to enable the watchdog. It has a weak internal pull-up.                                  |

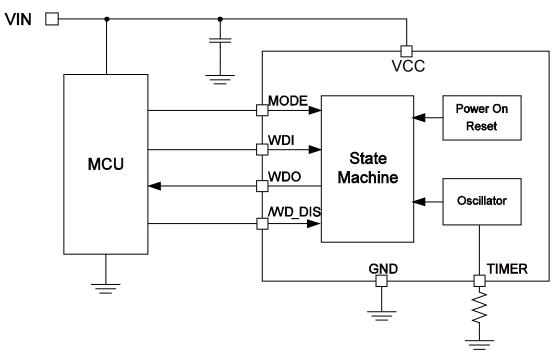

# **FUNCTIONAL BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

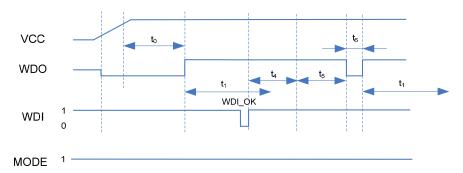

## **TIMING DIAGRAM**

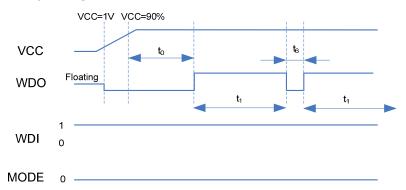

## Power-on reset and no sync signal

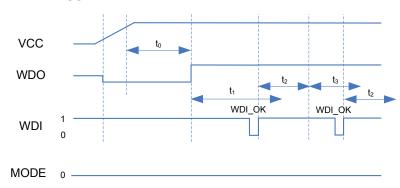

## Synchronized by WDI and triggered in open window (MODE=0, short window mode)

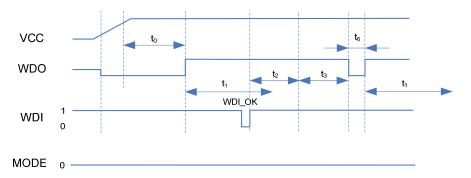

## Synchronized by WDI and no trigger signal (MODE=0, short window mode)

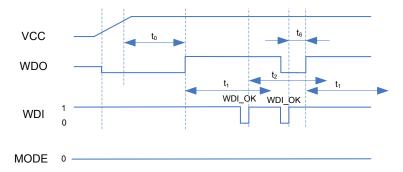

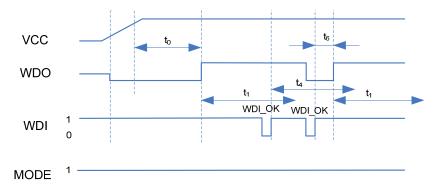

#### Synchronized by WDI and triggered in closed window (MODE=0, short window mode)

Note: When the WDI\_OK rising edge that comes at WDO is low, the  $t_6$  timer will be reset. Therefore, in the situation above, the WDO reset signal maintains a  $t_6$ +WDI\_OK time.

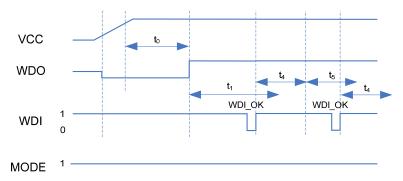

## Synchronized by WDI and triggered in open window (MODE=1, long window mode)

#### Synchronized by WDI and no trigger signal (MODE=1, long window mode)

# Synchronized by WDI and triggered in closed window (MODE=1, long window mode)

Note: When the WDI\_OK rising edge that comes at WDO is low, the  $t_6$  timer will be reset. Therefore, in the situation above, the WDO reset signal maintains a  $t_6$ +WDI\_OK time.

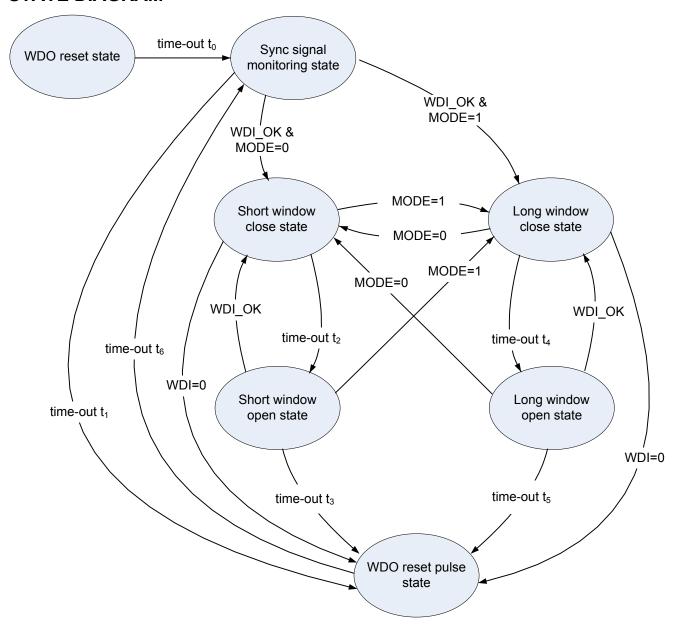

# **STATE DIAGRAM**

Note: The state diagram above does not include if a WDI error occurs.

#### **OPERATION**

#### **Supply Voltage**

$V_{\rm CC}$  = 5V +/-10% is recommended for normal operation. WDO is pulled low when Vcc rises to 1V or above. After Vcc rises to 4.65V (typically), WDO will remain at a low level for  $t_0$  to reset the MCU.

#### **TIMER**

Period T (µs):

$$T(\mu s) = 15.75 \times R_{TIMER}(k\Omega) + 73.5$$

$R_{TIMER}$  (k $\Omega$ ):

$$R_{TIMER}(k\Omega) = 0.063 \times T(\mu s) - 4.67$$

For example: R<sub>TIMER</sub>=51kΩ, T≈0.88ms

#### **Monitor MCU Synchronization Signal**

When the watchdog is in a "sync signal monitoring state," the following will occur:

- ♦ If the watchdog IC receives a WDI\_OK signal from the MCU within t₁ (WDI remains low for 10µs to 5ms), the timer will be reset, and the watchdog works in normal operation.

- ◆ If the watchdog does not receive the WDI\_OK signal from the MCU during t₁, it will generate a reset signal and go into "sync signal monitor state" again.

#### **Short Window Mode**

If the MCU and watchdog are synchronized correctly and MODE is low, the watchdog will work in short window mode:

- If WDI\_OK is received in a window close state (t<sub>2</sub>), the watchdog outputs a reset signal and goes into a sync signal monitoring state.

- ◆ If WDI\_OK is received in a window open state (t₃), the watchdog goes into a window close state. The MCU works in normal operation in this situation.

- If no WDI\_OK signal is received in t<sub>2</sub>+t<sub>3</sub>, the watchdog outputs a reset signal and goes into a sync signal monitoring state.

- If MODE is pulled high during short window mode, the watchdog will go into long window mode.

#### **Long Window Mode**

If the MCU and watchdog are synchronized correctly and MODE is high, the watchdog will operate in long window mode, and the following will occur:

- ◆ If WDI\_OK is received in a window close state (t₄), the watchdog outputs a reset signal and goes into a sync signal monitoring state.

- ◆ If WDI\_OK is received in a window open state (t₅), the watchdog goes into a window close state. The MCU works in normal operation in this situation.

- ◆ If no WDI\_OK signal is received in t₄+t₅, the watchdog outputs a reset signal and goes into a sync signal monitoring state.

- If MODE is pulled low during a long window mode, the watchdog will go into a short window mode.

#### Watchdog Disable

Pull /WD\_DIS low to disable the watchdog; pull it high to enable the watchdog. /WD\_DIS has a weak internal pull-up, so the watchdog is enabled if /WD\_DIS is left open.

#### **WDI Error**

If a WDI signal remains at a low level for longer than the maximum WDI\_OK pulse width, it is regarded as an error. When this error occurs, WDO is pulled down until WDI returns to a high level.

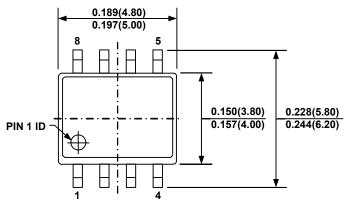

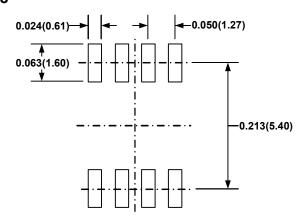

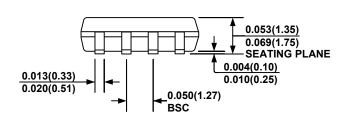

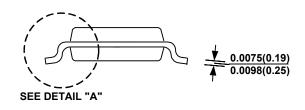

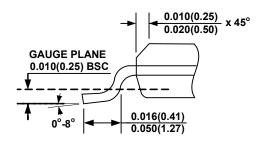

#### **PACKAGE INFORMATION**

# SOIC-8

#### **TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

#### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.