# One, Two and Four Channel Clock Transaltor

### **Features**

- Up to four independent clock channels

- Excellent jitter performance of 180 fs rms in 12 kHz to 20 MHz band meets jitter requirements of 10G/40G and 100G PHYs

- Three programmable ultra-low jitter synthesizers generate any frequency from 0.5 Hz to 900 MHz.

- One programmable general purpose synthesizer generates any clock from 0.5 Hz to 180 MHz

- 6 differential (CML) or 12 single ended (CMOS) ultralow jitter outputs plus two general purpose CMOS outputs

- Accepts up to 10 LVPECL/LVDS/HCSL/LVCMOS inputs

- Any input reference can be fed with clock, sync (frame pulse), clock /sync pair or clock modulated with sync pulse (embedded PPS ePPS and embedded PP2S ePP2S)

# Ordering Information ZL30611LDG6\* 100 Pin aQFN Trays ZL30612LDG6\* 100 Pin aQFN Trays ZL30614LDG6\* 100 Pin aQFN Trays \*Pb Free Tin/Silver/Copper Package size: 10 x 10 mm -40°C to +85°C

- Up to four programmable digital PLLs/NCOs with loop bandwidth from 14 Hz to 470 Hz synchronize to any clock rate from 1 kHz to 900 MHz and to clock plus sync pulse.

- Automatic hitless reference switching and digital holdover on reference fail with initial holdover accuracy better than 1 ppb with post holdover filter.

### **Applications**

- Synchronous Ethernet/Sonet/SDH timing and line cards

- Wireless Backhaul

- · Wireless Base stations

- Test Equipment

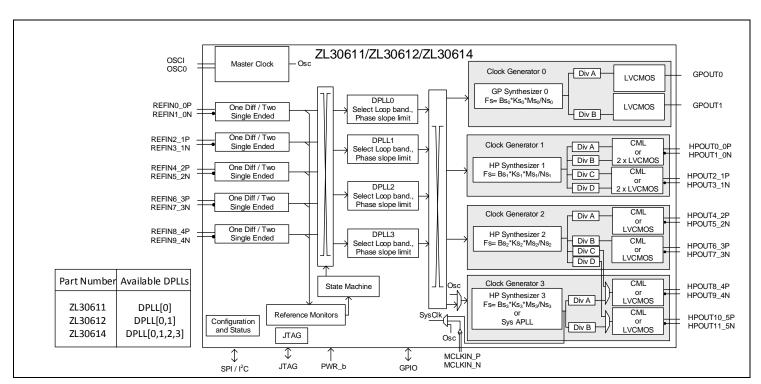

Figure 1. Functional Block Diagram

### 3 Feature List

### 3.1 General features

- Up to four independent clock channels

- Operates from a single crystal resonator or clock oscillator

- Configurable from SPI/I2C bus or from pre-configured flash memory

### 3.2 Electrical Clock Inputs

- Accepts up to 10 LVCMOS or 5 LVDS/HCSL/LVPECL/CML inputs

- Frequencies from 0.5 Hz to 180 MHz for LVCMOS

- Frequencies from 0.5 Hz to 900 MHz for LVDS/HCSL/LVPECL/CML

- Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities.

- o Each input reference has its own set of monitors which can be independently programmed.

- o Loss of signal (LOS)

- o Single Cycle Monitor (Triggers on glitches or variation in duty-cycle)

- Coarse Frequency Monitor

- o Precise Frequency Monitor

- Locks to gapped clocks

### 3.3 Electrical Clock Input-Output Special Formats

- Supports 64 kHz composite clocks with external glue logic

- Supports embedded pulse per second (ePPS) single wire for carrying high-speed clock & 1PPS

- Supports REF-SYNC pair, a combination of a high speed clock reference and a frame pulse sync pair

- Each output can generate clock, sync pulse, embedded pulse per second (ePPS) or embedded pulse per 2 seconds (ePP2S)

- Clock modulated sync feature helps in reducing number of clock lines on backplane and in addition provides equal delay for both clock and sync signals.

### 3.4 Electrical Clock Engine

- Digital PLLs filter jitter from 14 Hz up to 470 Hz

- Multiple modes of operation

- o Freerun

- Forced holdover

- Forced reference

- o Automatic

- o NCO

- Internal state machine automatically controls state

- o Locked

- Acquiring

- o Holdover

- Support for fast lock with lock times in seconds

- Support for hitless reference switching

- Internal, per DPLL, time of day counters maintaining full 48-bit seconds and 32-bit nanoseconds aligned to 1PPS rollover

- Holdover better than 0.01 ppb

- Full rate conversion between input and output clock frequencies

- Supports ITU-T G.823, G.824 and G.8261 for 2048 Kbit/s and 1544 Kbit/s interfaces

- Supports G.781 SETS

### 3.5 Electrical Clock Generation

- Four programmable synthesizers

- Precision Synthesizers

- o Each ultra-low jitter output can be independently set to be differential (CML) or two CMOS

- o Six CML outputs

- Generate clock rates from 0.5 Hz to 900 MHz

- Jitter performance of 180 fs rms (12 KHz 20 MHz)

- Meets OC-192, STM-64, 1 GbE & 10 GbE interface jitter requirements

- o Twelve LVCMOS outputs

- Generate clock rates from 0.5 Hz to 180 MHz

- Jitter performance of 290 fs rms (12 kHz 20 MHz)

- General Synthesizer

- Two LVCMOS outputs

- o Generate clock rates from 1 Hz to 180 MHz

- Jitter performance of 17 ps rms (12 kHz 20 MHz)

- Programmable output advancement/delay to accommodate trace delays or compensate for system routing paths

- Each output has its own power supply pin which can be hooked to 3.3V, 2.5V or 1.8V supplies. Outputs may be disabled to save power

# 4 Application

The only difference between ZL30611/ZL30612/ZL30614 is the number of DPLLs. The least significant digit in the part number assigns the number of available DPLLs.

### 4.1 Applications Examples

- Integrated basestation reference synchronization for air interfaces for

- GSM, WCDMA, TD-SCDMA, LTE and LTE-A

- FDD or TDD mobile technology

- femtocells, small cells (residential, urban, rural, enterprise), picocells and macrocells

- Mobile Backhaul NID, cell-site router, edge switch/router, microwave or access aggregation node

- EPON/GPON OLT and ONU/OLT

- DSLAM and RT-DSLAM

- 10 Gigabit line cards

- Synchronous Ethernet, 10 GBASE-R and 10 GBASE-W

- SONET/SDH, Fiber Channel, XAUI

### 4.2 Physical Layer - Chassis Architecture

ZL30611/ZL30612/ZL30614 provides up to four independent PLL channels which can synchronize to any input frequency from 0.5Hz up to 900MHz for clock/sync pair inputs and from 1 kHz to 900 MHz for clock only inputs. ZL30611/ZL30612/ZL30614 can generate any output frequency from 0.5Hz up to 180MHz for LVCMOS and up to 900MHz for CML outputs. Each channel is comprised of a DPLL and a Synthesizer.

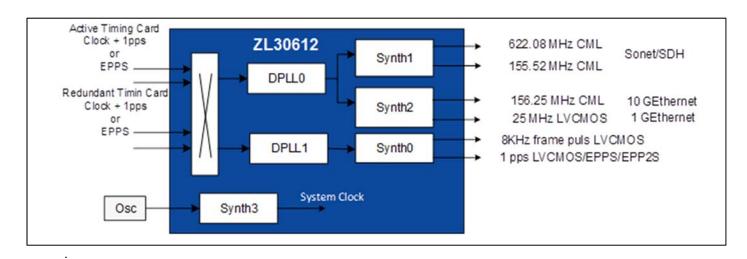

Typical application of ZL30611/ZL30612/ZL30614 is Synchronous Ethernet/Sonet/SDH line card synchronizer device as shown in **Error! Reference source not found.**. Line card synchronizer is responsible for:

- Provide hitless reference switching between active and redundant timing cards.

- Translate frequency from backplane clock to frequencies required by PHY devices.

- Filter jitter down to levels required by PHY devices.

- Provide holdover in case both active and redundant timing card fail.

For 1588 applications synchronize to sync plus clock (typically 1pps plus 10MHz) and generate 1pps signal. If the XO frequency is higher than 100MHz - 5%, Synthesizer 3 can be locked to any DPLL and used to generate any frequency. For fundamental mode oscillators (up to 50MHz) Synthesizer 3 needs to be used as an internal system clock generator.

Figure 2. System with timing redundancy

# 5 Product Family

There are several devices within the ZL30611/612/614 family. They are differentiated by the number of DPLL, as shown in

Table 1 · ZL3061x Product Family

| Product Number | Number of DPLL Channels | Number of Synthesizers |

|----------------|-------------------------|------------------------|

| ZL30611        | 1                       | 4                      |

| ZL30612        | 2                       | 4                      |

| ZL30614        | 4                       | 4                      |

devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

**Microsemi Corporate Headquarters** One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

**E-mail**: sales.support@microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization