# **MP111 Dying Gasp Storage and Release** Control IC

#### DESCRIPTION

The MP111 is a dying gasp storage and release controller. It charges storage capacitor from the input during normal operation. Once the storage capacitor is charged to the selected voltage, the charge is stopped, and the storage capacitor is separated from the input. The charging circuit maintains the storage voltage after the charge is completed.

The MP111 keeps monitoring the input voltage, and releases the charge from storage capacitor to input capacitor when the input voltage is lower than the selected release voltage. It regulates the input voltage to keep it close to release voltage for as long as possible.

The MP111 has built-in current limit circuit during the charging up of the storage capacitors. The storage and release voltage can be programmed to user's desired value by external resistors.

The MP111 comes in an SOIC-8 package and requires a minimum number of readily available standard external components.

#### **FEATURES**

- Wide 4.5V to 18V Input Operating Range

- 2.5A dumping current from Storage to VIN

- Built-in 250mA Current Limit for Charging **Storage Capacitor**

- User Programmable Storage and Release Voltage

- Dying Gasp FLAG Indicator

- Available in SOIC-8 package

# **APPLICATIONS**

- Cable/DSL/PON Modems

- Home Gateway

- Access Point Networks

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

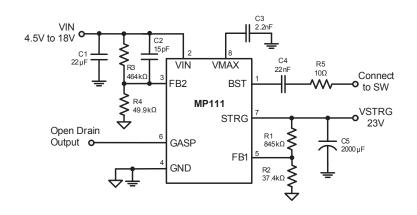

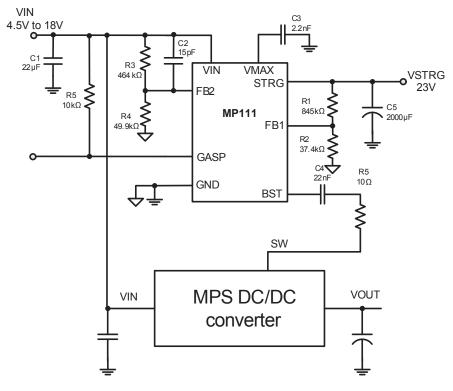

## TYPICAL APPLICATION

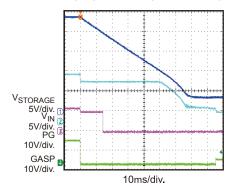

#### VSTORAGE Release

V<sub>STRG</sub>=23V, V<sub>RLES</sub>=10.2V, P<sub>RLES</sub>=5W

# ORDERING INFORMATION

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| MP111DS      | SOIC-8  | MP111       |

\* For Tape & Reel, add suffix –Z (eg.MP111DS–Z); For RoHS, compliant packaging, add suffix –LF (eg. MP111DS–LF–Z).

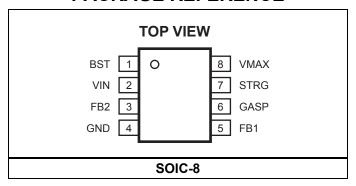

#### PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>IN</sub>                            | 0.3V to 22V                             |

|--------------------------------------------|-----------------------------------------|

| V <sub>BST</sub>                           |                                         |

| V <sub>BST</sub> -V <sub>IN</sub>          | 0.3V to 25V                             |

| V <sub>MAX</sub>                           | 0.3V to 42V                             |

| $V_{MAX}$ - $V_{IN}$                       | 0.3V to 25V                             |

| V <sub>STRG</sub>                          | 0.3V to 32V                             |

| V <sub>STRG</sub> -V <sub>IN</sub>         |                                         |

| V <sub>PG</sub> , V <sub>GASP</sub>        |                                         |

| All Other Pins                             |                                         |

| Junction Temperature                       | 150°C                                   |

| Lead Temperature                           | 260°C                                   |

| Continuous Power Dissipation               | (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                            | 1.2W                                    |

| Junction Temperature                       | 150°C                                   |

| Recommended Operating                      | Conditions (3)                          |

| Supply Voltage V <sub>IN</sub>             | 4.5V to 18V                             |

| Storage Voltage V <sub>STRG</sub>          |                                         |

| Vin to 2×\                                 |                                         |

| Operating Junction Temp. (T <sub>J</sub> ) |                                         |

|                                            |                                         |

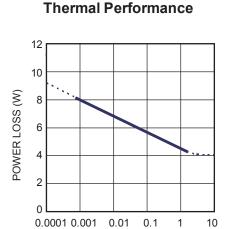

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |        |

|------------------------|-------------------------|-------------------------|--------|

| SOIC-8                 | 90                      | 45                      | . °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                                         | Symbol               | Condition                                                            | Min                   | Тур                    | Max                   | Units            |

|-------------------------------------------------------------------|----------------------|----------------------------------------------------------------------|-----------------------|------------------------|-----------------------|------------------|

| Input Supply Voltage Range                                        | V <sub>IN</sub>      |                                                                      | 4.5                   |                        | 18                    | V                |

| Supply Current (Shutdown)                                         | I <sub>IN</sub>      | V <sub>EN</sub> = 0V                                                 |                       | 1                      |                       | μA               |

| Supply Current (Quiescent)                                        | I <sub>IN</sub>      | V <sub>EN</sub> = 2V, V <sub>FB</sub> = 1.1V                         |                       | 300                    |                       | μΑ               |

| VIN Under Voltage Lockout Threshold Rising                        | INUVvth              |                                                                      | 3.0                   | 3.5                    | 4.0                   | V                |

| VIN Under Voltage Lockout<br>Threshold Hysteresis                 | INUV <sub>HYS</sub>  |                                                                      |                       | 350                    |                       | mV               |

| Feedback Voltage                                                  | $V_{FB}$             |                                                                      | 0.95                  | 1                      | 1.05                  | V                |

| Vstorage Refresh<br>Threshold-High                                | $V_{FB1\_H}$         |                                                                      |                       | V <sub>FB</sub> +0.025 | V <sub>FB</sub> +0.05 | V                |

| Vstorage Refresh<br>Threshold-Low                                 | $V_{FB1\_L}$         |                                                                      | V <sub>FB</sub> -0.05 | V <sub>FB</sub> -0.025 |                       | V                |

| Vstorage Refresh<br>Threshold-Hysteresis                          | V <sub>FB1_Hys</sub> |                                                                      |                       | 50                     |                       | mV               |

| Feedback Current                                                  | I <sub>FB</sub>      | V <sub>FB1</sub> = V <sub>FB2</sub> =1V                              |                       | 10                     |                       | nA               |

| GASP High Threshold                                               | VTHGASP              |                                                                      |                       | 1.05                   |                       | V <sub>FB2</sub> |

| GASP Low Threshold                                                | VTLGASP              |                                                                      |                       | 1                      |                       | $V_{\text{FB2}}$ |

| GASP Delay                                                        | GASPTd               |                                                                      |                       | 2                      |                       | μs               |

| GASP Sink Current<br>Capability                                   | VGASP                | Sink 4mA                                                             |                       | 0.4                    |                       | V                |

| GASP Leakage Current                                              | IGASP_LEAK           | VGASP=3.3V                                                           |                       | 10                     |                       | nA               |

| Input Inrush Current Limit for Charging Storage Capacitor         | IPRECHARGE_LIMIT     | V <sub>IN</sub> =12V, Charging<br>Cstorage from 0 to V <sub>IN</sub> |                       | 0.25                   |                       | Α                |

| Current limit for Dumping Charge from CSTORAGE to $V_{\text{IN}}$ | IDUMP_LIMIT          |                                                                      |                       | 2.5                    |                       | А                |

| Thermal Shutdown (5)                                              | Tsp                  |                                                                      |                       | 150                    |                       | °C               |

| Thermal Shutdown Hysteresis (5)                                   | Тнүѕ                 |                                                                      |                       | 30                     |                       | °C               |

#### Notes:

5) Guaranteed by design.

# **PIN FUNCTIONS**

| SOIC-8<br>Pin # | Name | Description                                                                                                                                                                               |

|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | BST  | Bootstrap. A capacitor and a resistor in series connected between this pin and DC/DC converter's SW node is required to charge storage capacitor.                                         |

| 2               | VIN  | Supply Voltage. The MP111 operates from a +4.5V to +18V input rail. Input decoupling capacitor is needed to decouple the input rail.                                                      |

| 3               | FB2  | Feedback to set release voltage.                                                                                                                                                          |

| 4               | GND  | System Ground. This pin is the reference ground of the regulated output voltage. For this reason care must be taken in PCB layout. Suggested to be connected to GND with copper and vias. |

| 5               | FB1  | Feedback to set storage voltage.                                                                                                                                                          |

| 6               | GASP | Open drain output to indicate dying gasp operation is active.                                                                                                                             |

| 7               | STRG | Connect to storage capacitor for dying gasp storage and release operation.                                                                                                                |

| 8               | VMAX | Internal Supply. A 2.2nF ceramic capacitor is required for decoupling.                                                                                                                    |

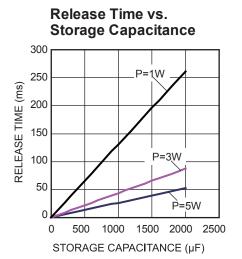

# TYPICAL PERFORMANCE CHARACTERISTICS

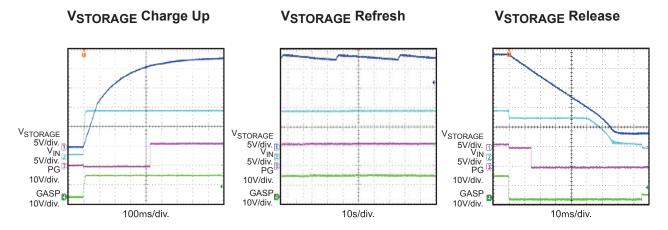

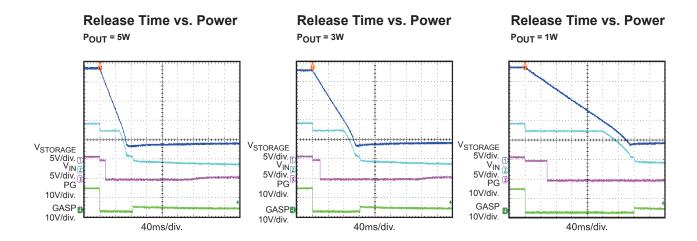

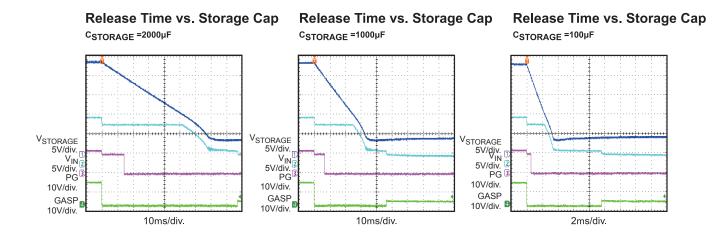

$V_{\text{IN}}$  = 12V,  $V_{\text{STORAGE}}$  = 23V,  $V_{\text{RELEASE}}$ =10.2V, For DCDC Converter:  $P_{\text{OUT}}$ =5W,  $V_{\text{OUT}}$ =3.3V,  $T_{\text{A}}$  = +25°C, unless otherwise noted.

MAXIMUM HOLD UP TIME (s)

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{STORAGE}$  = 23V,  $V_{RELEASE}$ =10.2V, For DCDC Converter:  $P_{OUT}$ =5W,  $V_{OUT}$ =3.3V,  $T_A$  = +25°C, unless otherwise noted.

© 2016 MPS. All Rights Reserved.

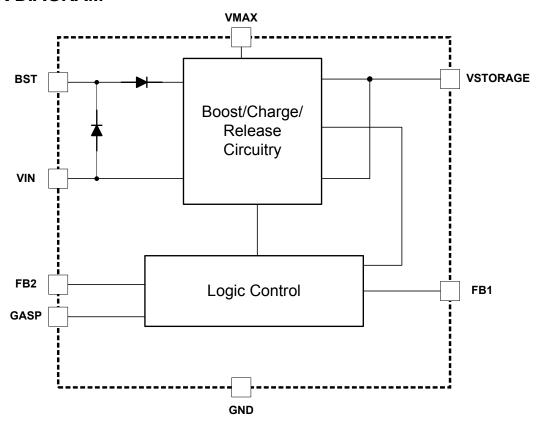

# **BLOCK DIAGRAM**

Figure 1 – Functional Block Diagram

#### **OPERATION**

MP111 is a dying gasp storage and release control IC. It charges the storage capacitors from input supply during power start up and keeps refreshing the storage voltage at a regulated value during normal operation. MP111 continuously monitors the input voltage. Once the input voltage is lower than the programmed release voltage in case of losing input power, it releases the charge from the storage capacitors to input, and keeps the input voltage regulated to the release voltage for as long as possible. It allows the system to respond to input power failure.

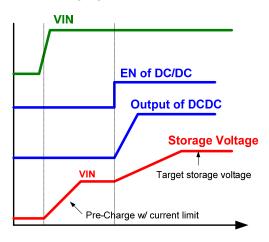

#### Start-Up

During the power start-up, there are two periods to charge the storage capacitors. In the first period, the MP111 pre-charges the large storage capacitors from 0 to nearly VIN with built-in inrush current limit. Once the storage voltage is close to the input voltage, the storage voltage is boosted and regulated at target voltage.

The BST pin of MP111 should connect to the DCDC switch node. Only after the DCDC is enabled, the MP111 will start boosting. Figure 2 shows the charging build-up process of MP111.

Figure 2 - Timing of Charging

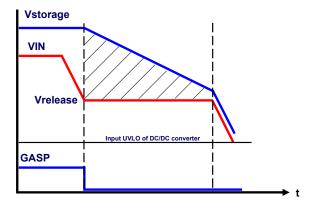

#### Release

MP111 keeps monitoring the input voltage. Once the input voltage is lower than selected release voltage in case of losing input power, MP111 moves the charge from high voltage storage capacitor to low input voltage capacitor. The release voltage can be determined by choosing appropriate input resistance divider. The maximum LDO release current can be as high as 2.5A. Until the storage capacitor voltage is near the input voltage, the input voltage loses its regulation and reduces further. A conceptual release process of MP111 is shown in Figure 3.

Figure 3 - Timing of Releasing

# **Gasp Indicator**

When the FB2 voltage, feedback voltage for the input power, is higher than  $1.05 \text{XV}_{\text{FB2}}$ , the GASP pin will be pulled high. Connect a resistor across VIN and GASP can drive GASP high. When the FB voltage is lower than  $1.00 \text{XV}_{\text{FB2}}$ , the GASP voltage will be internally pulled low. GASP voltage can be used as communication indicator signal which states input power availability.

## **APPLICATION INFORMATION**

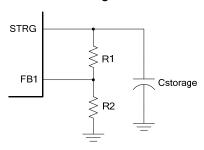

#### **SET STORAGE VOLTAGE**

The storage voltage can be set by choosing appropriate external feedback resistors R1 and R2 which is shown in Figure 4.

Figure 4 – Feedback Circuit for Storage Voltage

The storage voltage is determined by:

$$V_{\text{STORAGE}} = (1 + \frac{R1}{R2}) \times V_{\text{FB1}}$$

Here is the example, if the storage voltage is set to be 20V, choose R2 to be  $40k\Omega$ , R1 will be then given by:

$$R1 = \frac{40k\Omega \times (20 - V_{FB2})}{V_{FB2}} = 760k\Omega$$

Table 1 lists the recommended resistors for different storage voltages.

Table 1 – Resistor Selection for Different Storage Voltages

| V <sub>STORAGE</sub> (V) | R1 (kΩ) | R2 (kΩ) |

|--------------------------|---------|---------|

| 15                       | 750     | 53.2    |

| 19                       | 750     | 41.6    |

| 23                       | 850     | 37.4    |

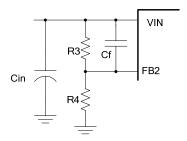

# Select Release Voltage and Input Capacitors The release voltage can be set by choosing external feedback resistors R3 and R4 which is shown in Figure 5.

Figure 5 – Release Feedback Circuit Similarly, the release voltage is set by:

$$V_{\text{RELEASE}} = (1 + \frac{R3}{R4}) \times V_{\text{FB2}}$$

However, the selection of R3 and R4 not only determines the release voltage, but impacts the stability. Generally, choosing R3 to be  $300{\sim}500k\Omega$  is recommended for a stable performance with  $47\mu F$  Cin. Table 2 lists the recommended resistors setup for different release voltages.

Table 2 – Resistor Selection for Different Release Voltages

| V <sub>RELEASE</sub> (V) | R1<br>(kΩ) | R2<br>(kΩ) | Cf<br>(pF) | Cin<br>(µF) |

|--------------------------|------------|------------|------------|-------------|

| 11                       | 475        | 47.5       | 15         | 47          |

| 10.2                     | 464        | 49.9       | 15         | 47          |

| 9.0                      | 324        | 40.2       | 15         | 47          |

### **Select Storage Capacitor**

The Storage Capacitor is for energy storage during normal operation and the energy will be released to VIN in case of losing input power. Typically, a general purpose electrolytic capacitor is recommended.

The voltage rating of storage capacitor needs to be higher than the targeted storage voltage. The voltage rating of storage capacitor can be fully utilized since the voltage on storage capacitor is very stable during normal operation. There will be less ripple current/voltage for most of the time during normal operation. The ripple current rating of storage cap can be less consideration.

The needed capacitance is dependent on how long the dying gasp time based on typically

application. Assume the input release current is  $I_{RELEASE}$  when input voltage is regulated at  $V_{RELEASE}$  for the DCDC converter. The storage voltage of MP111 is  $V_{STORAGE}$ , and the required dying gasp time is  $T_{DASP}$ . The necessary storage capacitance can be calculated as following equation:

$$Cs = \frac{I_{\text{RELEASE}} \times T_{\text{DASP}}}{V_{\text{STORAGE}} - V_{\text{RELEASE}}}$$

If  $I_{RELEASE}$ =1A,  $T_{D}$ =20ms,  $V_{STORAGE}$ =20V,  $V_{RELEASE}$ =10V, the needed storage capacitance is 2000 $\mu$ F. Generally, the storage capacitance should be chosen a little bit large to avoid capacitance reduction at high voltage offset.

In typical xDSL applications using a 12V input supply, it is recommended to set the storage voltage higher than 20V to fully utilize the high voltage energy and minimize storage capacitance requirements. Generally, a 25V rated electrolytic capacitor can be used. The lifetime of electrolytic capacitors can be severely impacted by both environmental and electrical factors. One of the most critical electrical factors is the AC RMS ripple current through the capacitor which leads to increased capacitor core temperatures. Normally, for typical industrial uses, it is recommended to derate the capacitor voltage rating by as much as 70%-80%. For example, a 25V rated electrolytic capacitor would be used for a 16V to 20V application.

However, since the MP111 tightly regulates the storage voltage, the storage capacitor almost has no AC ripple current going through it. The resulting refresh rate of the MP111 is very low which allows customers to safely use a 90% capacitor derating <sup>(6)</sup>. For example, a 25V electrolytic capacitor, can safely handle a storage voltage of up to 22V. Table 3 is some recommended storage electrolytic capacitors which can be used in typical xDSL application

### **PCB Layout Guide**

PCB layout is very important to achieve stable operation. Please follow these guidelines and take the EVB board layout for references.

- Connect the BST pin as close as possible to the SW node of DCDC converter through a resistor and a small ceramic capacitor. Try to avoid interconnect the feedback path.

- Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- Keep the connection of the storage capacitors and STRG pin as short and wide as possible.

Table 3 - Recommended Storage Capacitors

| Part #          | Vender    | Capacitance | Voltage | Operating Temp |

|-----------------|-----------|-------------|---------|----------------|

| 25ME1500WX      | Sanyo     | 1500µF      | 25V     | -40 to +105°C  |

| PEH526HAB4270M3 | Kemet     | 2700µF      | 25V     | -40 to +105°C  |

| EEUFR1E152B     | Panasonic | 1500µF      | 25V     | -40 to +105°C  |

#### Notes

6) "Applying voltage does not affect the life time because the self heating by applying voltage can be ignored", from Sanyo.

# TYPICAL APPLICATION CIRCUITS

Figure 6 - MP111 Application Circuit

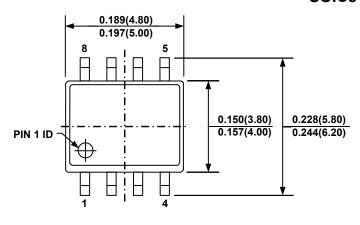

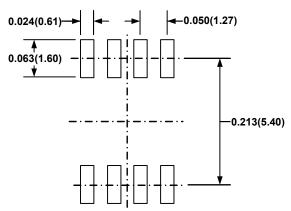

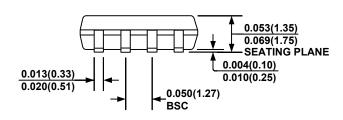

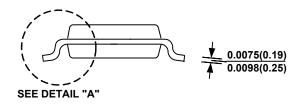

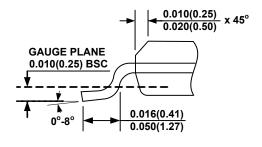

## PACKAGE INFORMATION

# SOIC8

#### **TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

#### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.