- About us

- Request a Quote

- English

-

Select the national language currency you need to view

Microchip goes 64bit with RISC-V, and plans Arm

Although, “future PIC64 families will include devices based on RISC-V or Arm architectures”, said the company.

PIC64-HPSC is the family name of the space processors, which have come out of a 2022 deal with NASA to develop “a high-performance space-flight computing [HPSC] processor that could provide at least 100 times the computational capacity of current spaceflight computers”, said Microchip.

PIC64-HPSC is the family name of the space processors, which have come out of a 2022 deal with NASA to develop “a high-performance space-flight computing [HPSC] processor that could provide at least 100 times the computational capacity of current spaceflight computers”, said Microchip.

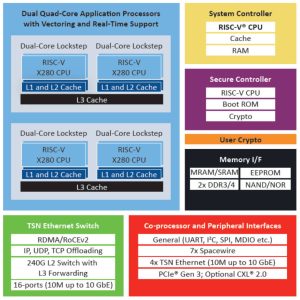

The company has licensed SiFive’s X280 64bit cores for this HPSC family, which will run at up to 1GHz to deliver 26,000Dmips.

It has included vector processing hardware to accelerate artificial intelligence and machine learning to the tune of 2Top/s of int8 arithmetic, or 1Tflop/s of bfloat16.

On top of this is a 64bit SiFive S7 system monitoring core.

“The radiation-hardened PIC64-HPSC RH is designed to give autonomous missions the local processing power to execute real-time tasks such as rover hazard avoidance on the Moon’s surface, while also enabling long-duration, deep-space missions like Mars expeditions requiring extremely low-power consumption while withstanding harsh space conditions,” according to Microchip. “For the commercial space sector, the radiation-tolerant PIC64-HPSC RT is designed to meet the needs of low-Earth-orbit constellations where system providers must prioritise cost over longevity, while also providing fault tolerance that is vital for round-the-clock service reliability and the cyber-security of space assets.”

For high-reliability processing, dual-core lock-step operation operation is supported (diagram above), and SiFive’s WorldGuard virtualisation hardware is implemented for code isolation and data protection.

Microchip describes its in-built security as “defence-grade”, and said that the IC “implements defence-in-depth security with support for post-quantum cryptography and anti-tamper features”.

For data transfer, the chips will have PCIe Gen 3 and CXL (compute express link) 2.0 with x4 or x8 configurations, RMAP-compatible SpaceWire ports with internal routers, and a 240Gbit/s TSN (time-sensitive networking) Ethernet switch for 10Gbit Ethernet.

RDMA (remote direct memory access) over converged Ethernet (RoCEv2) is hardware accelerated for low-latency transfer from remote sensors.

64bit quad-core RISC-V

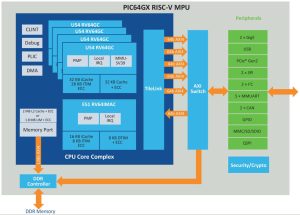

The industrial quad core RISC-V processors are called the PIC64GX family, and aimed at real-time applications such as embedded vision and machine learning.

They will be available in packaging that is pin-compatible with the company’s existing PolarFire FPGAs.

Microchip picked SiFive’s U54 core, and is rating the ICs at 5,000Dmips. It has not included vector hardware, but has included secure boot and crypto acceleration.

System monitoring is provided by a 64bit SiFive E51 core in place of the space processor’s S7.

The main cluster can be split, with some cores set for deterministic real-time execution, while the others are configured for fastest Linux application processing.

GX1000 is the first IC from this family, due to sample this month, followed in March next year by GX1100 which will be a version boosted with AI inferencing hardware.

Development support will come from hardware and software including the ‘PIC64GX Curiosity Evaluation Kit’ and, for users of Microsoft Visual Studio Code, ‘MPLAB Extensions for VS Code’.

“PIC64 MPUs are also supported by Linux4Microchip resources and Linux distributions such as Canonical Ubuntu, the Yocto Project and Buildroot with support for Zephyr RTOS and associated software stacks,” said Microchip, adding that PIC64-HPSC space processors will “be supported by a space-grade ecosystem that encompasses flight-capable industry-standard single-board computers and a community of software partners. Early members are SiFive, Moog, Ideas-TEK, Ibeos, 3D Plus, Micropac, Wind River, Linux Foundation, RTEMS, Xen, Lauterbach and Entrust”.

PIC64-HPSC evaluation hardware is being developed, and samples of the ICs will be be shipped to selected companies in Q1 next year.

What manufacturing processes has Microchip picked for its first 64bit processors?

“PIC64GX is 28nm from UMC, and the PIC64-HPSC is fabricated using GlobalFoundries’ 12nm 12LP+ process node, which incorporates finFET technology,” Microchip marketing director Venki Narayanan (right) told Electronics Weekly. “GlobalFoundries’ is an on-shore fab, accredited by US government.”

“PIC64GX is 28nm from UMC, and the PIC64-HPSC is fabricated using GlobalFoundries’ 12nm 12LP+ process node, which incorporates finFET technology,” Microchip marketing director Venki Narayanan (right) told Electronics Weekly. “GlobalFoundries’ is an on-shore fab, accredited by US government.”

Will the octa-core processor make it down to Earth?

“You can anticipate Microchip to expand the PIC64 portfolio to include terrestrial PIC64 devices with octa-cores in the future,” said Narayanan.

More will be revealed about the space processors next week at the IEEE Space Compute Conference in Mountain View (15-19 July 2024).